### АВТОМАТИКА И ЭЛЕКТРОНИКА

УДК 621.382+621.396.6

### ОСОБЕННОСТИ ОБРАЗОВАНИЯ ПОМЕХ ПРИ ПЕРЕКЛЮЧЕНИИ КМОП-ЭЛЕМЕНТА И ВОЗДЕЙСТВИИ ИОНИЗИРУЮЩЕЙ ЧАСТИЦЫ

© 2020 г. В. Я. Стенин<sup>1,2,\*</sup>, Ю. В. Катунин<sup>1,\*\*</sup>

<sup>1</sup> НИИ системных исследований Российской академии наук, Москва, 117218, Россия

<sup>2</sup> Национальный исследовательский ядерный университет "МИФИ", Москва, 115409, Россия

\*e-mail: vystenin@mephi.ru \*\*e-mail: katunin@cs.niisi.ras.ru Поступила в редакцию 18.06.2020 г. После доработки 26.06.2020 г. Принята к публикации 08.09.2020 г.

Приводятся результаты моделирования элементов И и ИЛИ в составе мажоритарного элемента при переключении по входам и одновременном сборе заряда с трека частицы. Моделирование проведено с использованием 3D TCAD физических моделей КМОП-транзисторов по проектной норме 65-нм объемной технологии с мелкой траншейной изоляцией групп транзисторов при треках с линейным переносом энергии 60 МэВ см²/мг. Установлено, что начало переключения элементов И и ИЛИ по входам практически не влияет на зависимость переходных процессов образования импульсов помех на выходе элемента при сборе заряда с трека. Импульсы помехи сдвигаются во времени на интервал времени, равный смещению момента образования трека относительно момента переключения элемента по входам. Сбор заряда с трека приводит к переключению элемента до изменения входных сигналов, либо к дополнительной задержке переключения. Длительности импульсов помех на выходах элементов И и ИЛИ заключены в пределах от 12 пс до 345 пс. При этом сохраняется практически неизменной длительность импульса помехи для конкретных точек входа трека в общую область расположения транзисторов. При этом длительность импульса помехи остается практически неизменной для каждой конкретной точки входа трека в общую область расположения транзистора независимо от момента формирования трека.

*Ключевые слова:* импульс помехи, логический элемент, моделирование, одиночная частица, сбор заряда, трек

**DOI:** 10.1134/S2304487X20030098

#### 1. ВВЕДЕНИЕ

КМОП комбинационные логические элементы являются основой кодирующих, декодирующих устройств и мажоритарной логики. Моделирование эффектов воздействия одиночных ионизирующих частиц с использованием приборных физических моделей (physics-based device models) как двумерных (2D), так и трехмерных (3D), посвящен ряд обобщающих работ, в которых моделированием предсказано [1] снижение помехоустойчивости КМОП-логики по объемной технологии до уровня линейной передачи энергии частицы на трек 2 МэВ см<sup>2</sup>/мг при понижении проектной нормы до 100 нм, а также эффект перехода NMOП-транзисторов в инверсный режим смещения [2] и увеличение длительности импульса помехи до 300-500 пс при 30 МэВ см<sup>2</sup>/мг. При проектных нормах менее 100 нм в КМОПлогике проявилось влияние диффузионного переноса носителей заряда, индуцированных на треке, на смежные элементы. При этом совместный сбор заряда может снижать длительности импульсных помех [4]. Проведено моделирование [5] основных характеристик мажоритарного элемента на основе элементов И и ИЛИ с проектной нормой объемный 65-нм КМОП с мелкой траншейной оксидной изоляцией групп транзисторов.

Целью данной работы является моделирование средствами TCAD базовых элементов с логикой И и ИЛИ в составе мажоритарного элемента по проектной норме объемный 65-нм КМОП с мелкой траншейной изоляцией транзисторов для получения количественных оценок временных параметров импульсов помех при одновременном переключении элементов по входам и сборе заряда с трека одиночной частицы.

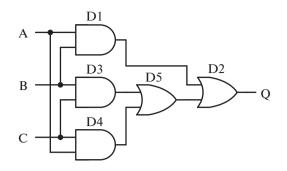

Рис. 1. Функциональная схема мажоритарного элемента на логических элементах И и ИЛИ.

#### 2. ТРОЙНОЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ НА И и ИЛИ ЭЛЕМЕНТАХ

#### 2.1. Схема и топологии комбинационных элементов

На рис. 1 приведен вариант функциональной схемы тройного мажоритарного элемента на основе двухвходовых КМОП-элементов И (D1, D3, D4) и ИЛИ (D2, D5).

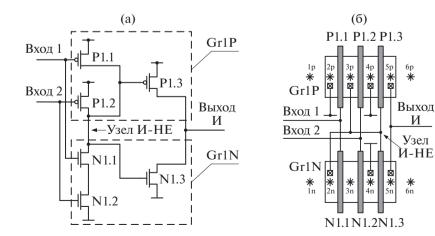

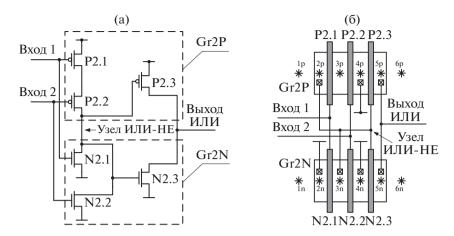

На рис. 2 приведены схема (рис. 2а) и эскиз топологии (рис. 2б) двухвходовой КМОП логический элемент И. Первая цифра в обозначениях транзисторов на рис. 2 соответствует номеру элемента на рис. 1, а вторая — номеру транзистора в элементе. Элемент И (рис. 2) состоит из логического элемента И-НЕ на транзисторах N1.1, N1.2, P1.1, P1.2 и инвертора на транзисторах N1.3, P1.3. На рис. 3 приведены схема (рис. 3а) и эскиз топологии (рис. 36) двухвходового КМОП логического элемента ИЛИ (рис. 3) состоит из элемента ИЛИ-НЕ на транзисторах N2.1, N2.2, P2.1, P2.2 и инвертора на транзисторах N2.3, P2.3.

Области кремния на эскизах топологии на рис. 26 и рис. 36, в которых выполнены МОП-

транзисторы элементов, ограничены прямоугольниками, которые окружены мелкой траншейной изоляцией диэлектриком (диоксидом кремния) глубиной 400 нм; полоски со штриховкой обозначают затворы транзисторов, звездочками отмечены точки входа треков одиночных частиц.

Элемент И (рис. 2) состоит из группы NMOПтранзисторов Gr1N и группы РМОП-транзисторов Gr1P. Аналогично элемент ИЛИ (рис. 3) состоит из группы NMOП-транзисторов Gr2N и группы РМОП-транзисторов Gr2P. Группы транзисторов Gr1N, Gr2N, Gr1P, Gr2P выполнены в областях кремния размером 885 нм × 400 нм, окруженных мелкой траншейной изоляцией глубиной 400 нм (прямоугольное обрамление транзисторов на рис. 26 и 36 показывает границы мелкой траншейной изоляции).

#### 2.2. Особенности моделирования сбора заряда с трека частицы

В работе проведено гибридное TCAD-SPICE моделирование КМОП мажоритарного элемента (рис. 1), при котором средствами ТСАД моделировались процессы генерации носителей заряда при передаче им энергии с трека в кремнии и процессы сбора заряда транзисторами в элементах D1 (И) и D2 (ИЛИ). Средствами SPICE моделировались характеристики двух элементов И (D3, D4) и элемента ИЛИ D5, которые обеспечивали перелачу сигналов на вхол элемента ИЛИ D2.

Использованы 3D TCAD физические модели КМОП-транзисторов [6] по проектной норме 65-нм КМОП объемной технологии. Как тестовое воздействие приняты треки частиц по нормали к поверхности приборной части модели элемента. Звездочками на рис. 2 и 3 отмечены точки входа треков частиц в области транзисторов. Ши-

И

Узел

Рис. 2. Комбинационный КМОП-элемент И: (а) схема элемента; (б) эскиз топологии.

Рис. 3. Комбинационный КМОП-элемент ИЛИ: (а) схема элемента; (б) эскиз топологии.

рина каналов транзисторов элементов И и ИЛИ равна 400 нм. Конструкции элементов И и ИЛИ состоят из транзисторов, выполненных в кремниевых областях, окруженных мелкой траншейной изоляцией с глубиной 400 нм (shallow trench isolation — STI). Области NМОП- и РМОП-транзисторов разделены охранными полосами для вывода неравновесных зарядов на шину питания и общую шину.

Полные размеры 3D приборной структуры составляют 6.4 мкм  $\times$  10.9 мкм при толщине подложки 3.0 мкм. Энергетическая составляющая генерации заряда на треке характеризуется линейной передачей энергии частицей на трек — (linear energy transfer — LET). При моделировании использовались треки с LET = 60 МэВ см²/мг. Результаты 3D TCAD-моделирования получены с использованием симулятора Sentaurus Device при температуре 25°C и напряжении питания 1.0 В.

#### 3. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ ИМПУЛЬСНЫХ ПОМЕХ В ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

Алгоритм работы тройного мажоритарного элемента заключается в получении выходного сигнала, который соответствует совпадению как минимум двух входных сигналов из трех. В этом случае два сигнала управляют правильным переключением только одного из трех элементов И. Для получения достоверных данных о влиянии импульсов помех на выход мажоритарного элемента достаточно моделирования средствами TCAD этого входного элемента И и следующего в цепочке элемента ИЛИ, а именно двух элементов D1, D2 (рис. 1) с двумя вариантами входных сигналов: A = B = C = 0 и A = B = 1, C = 0 (или A = B = C = 1).

Как области входа трека одиночной частицы выбраны следующие области:

- 1) область стока транзистора N1.1 группы Gr1N элемента И (точка входа трека 2n на рис. 2б);

- 2) область истока транзистора P1.1 группы Gr2P элемента И (точка входа трека 2р на рис. 2б);

- 3) область общих стоков транзисторов N2.1, N2.2 группы Gr2N элемента ИЛИ (точка входа трека 3n на рис. 36);

- 4) область стока транзистора P2.1 и истока транзистора P2.2 группы Gr2P (точка входа трека 3р на рис. 36).

Зависимости напряжений на узлах элемента И получены для точек входа трека 2n, 2p, а для элемента ИЛИ для точек входа трека 3n, 3p, направления треков по нормали к поверхности кристалла, линейная передача энергии на трек LET =  $60~{\rm M}{\rm 9B}~{\rm cm}^2/{\rm Mr}$ , образование трека в моменты  ${\rm t}_{\rm TP}=100~{\rm nc}$ ,  $160~{\rm nc}$  и 220 пс. Переключение мажоритарного элемента по входам при  ${\rm t}_{\rm ПEP}=200~{\rm nc}$ . Трек с  ${\rm t}_{\rm TP}=220~{\rm nc}$  образуется при переключении элемента по входам.

### 3.1. Сбор заряда с трека NMOП-транзисторами группы Gr1N элемента И D1

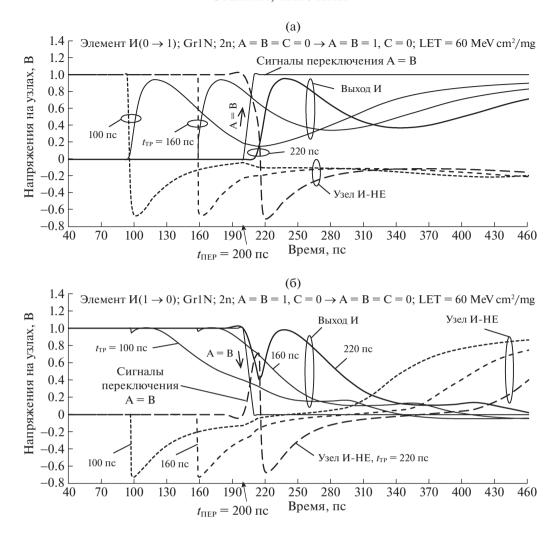

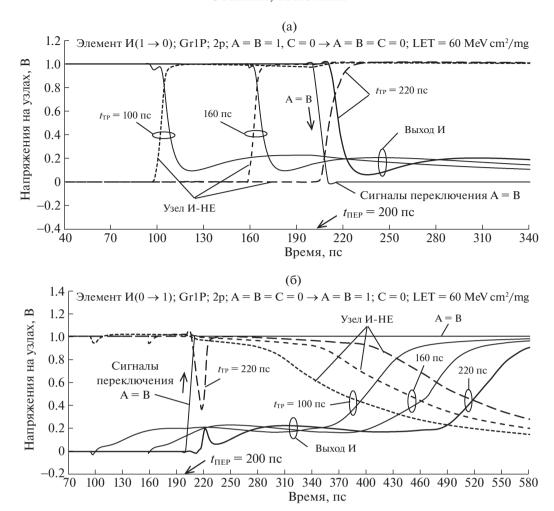

На рис. 4 приведены зависимости напряжений на узлах элемента N для точки входа трека 2n группы Gr1N, транзисторы которой выполнены в кремниевой подложке P-типа проводимости в общей для этих транзисторов области кремния (рис. 26). На рис. 4a приведены зависимости при исходных сигналах на входах элемента A=B=C=0 с переключением на A=B=1, C=0; а на рис. 46 при начальных сигналах на входах элемента A=B=1, C=0 с переключением на A=B=1 C=0.

**Рис. 4.** Зависимости напряжений на узлах элемента И мажоритарного элемента при образовании трека с LET =  $60~{\rm M} \cdot {\rm B} \times {\rm cm}^2/{\rm Mr}$  с точкой входа  $2 {\rm n}$  в группу транзисторов Gr1N, возникновение трека при  ${\rm t}_{\rm TP} = 100~{\rm nc}$ ,  $160~{\rm nc}$  и  $220~{\rm nc}$ ; при  ${\rm t}_{\rm \Pi EP} = 200~{\rm nc}$  переключение входов: (а) из  ${\rm A} = {\rm B} = {\rm C} = 0$  в  ${\rm A} = {\rm B} = 1$ ,  ${\rm C} = 0$ ; (б) из  ${\rm A} = {\rm B} = 1$ ,  ${\rm C} = 0$  в  ${\rm A} = {\rm B} = {\rm C} = 0$ .

Два семейства зависимостей на рис. 4а и 46 соответствуют трекам через одну точку входа 2n в сток транзистора N1.1 узла U-HE для двух вариантов переключения элемента: из  $0 \to 1$  и из  $1 \to 0$ . В обоих случаях в момент образования трека происходит переход цепочки двух  $NMO\Pi$ -транзисторов N1.1, N1.2 в инверсное смещение с образованием на узле U-HE импульса отрицательной полярности со значением экстремума напряжения — (0.66-0.7) В.

После перехода транзисторов N1.1, N1.2 в инверсное смещение инвертор переключается и затем его запертый NMOП-транзистор начинает собирать заряд с того же трека в группе Gr1N и напряжение на выходе инвертора (выходе элемента И) начинает снижаться. В случае режима переключения  $0 \rightarrow 1$  изменение напряжения до 1 В на

выходе И фактически осуществляет опережающее переключение элемента при треках с  $t_{TP}=100$  пс и 160 пс до смены сигналов на входах элемента. При этом после опережающего переключения сбор заряда с трека запертым NMOП-транзистором инвертора формирует импульс помехи отрицательной полярности (рис. 4а) с амплитудой 0.6-0.8 В. Во втором случае (рис. 4б) при переключении выхода И из  $1 \rightarrow 0$  сбор заряда NMOП-транзистором инвертора переводит элемент И в состояние логического нуля "0" с дополнительно увеличенной задержкой на выходе.

#### Переключение элемента H из $0 \rightarrow 1$ с опережением

При опережающем переключении выхода И импульс помехи ("просадка" напряжения на вы-

ходе) имеет одинаковые зависимости во времени и длительность 188 пс по уровню 0.7 В от напряжения на общей шине элемента для всех треков с  $t_{TP}=100$  пс, 160 пс и 220 пс (см. рис. 4а). Длительности задержек переключения относительно момента возникновения трека составляет 9 пс и 7 пс для треков с  $t_{TP}=100$  пс и 160 пс. Относительно момента начала переключения входов при  $t_{ПЕР}=200$  пс задержки опережающего переключения имеют отрицательные значения  $t_{3Д.ПЕР}=-91$  пс при  $t_{TP}=100$  пс и  $t_{3Д.ПЕР}=-33$  пс при  $t_{TP}=160$  пс. При треке с  $t_{TP}=220$  пс переключение происходит с задержкой  $t_{3Д.ПЕР}=22$  пс относительно изменения входных сигналов при  $t_{ПЕР}=200$  пс, но также с импульсом помехи на выходе.

### Переключение элемента H из $1 \to 0$ с дополнительной задержкой

При переключении входов из  $1 \to 0$  NМОПтранзисторы узла И-НЕ запираются, а транзисторы РМОП открываются, но на емкости узла И-НЕ сохраняется напряжение отрицательной полярности (см. рис. 46), что сохраняет запертым NМОП-транзистор инвертора при треках с  $t_{TP} = 100$  пс и 160 пс с напряжениями, которые были до переключения входов. После чего напряжение на выходном узле И продолжает снижаться до уровня логического нуля за счет сбора заряда с трека.

В случае образования трека при  $t_{TP} = 220$  пс после переключения сигналов на входах элемента при  $t_{\Pi EP} = 200$  пс, то переключение по входам вызывает снижение напряжения на выходе инвертора и выходе И до 0.4 В в интервале времени до 220 пс, когда образуется трек. Одновременно на узле И-НЕ (рис. 46) образуется импульс отрицательной полярности при сборе заряда NMOПтранзисторами узла, который переключает выход инвертора до 0.98 В, запирая NMOПтранзистор до 0.98 В, запирая NMOПтранзистор инвертора, который, собирая заряд с трека, снижает напряжение на выходе И до уровня логического нуля. В итоге задержки переключения составляют  $t_{3Д.\Pi EP} = 20$  пс, 48 пс и 107 пс для треков с  $t_{TP} = 100$  пс, 160 пс и 220 пс.

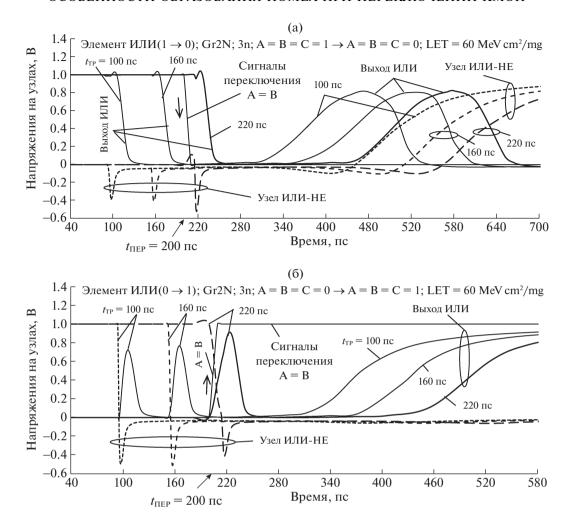

### 3.2. Сбор заряда с трека РМОП-транзисторами группы Gr1P элемента И D1

На рис. 5 приведены зависимости напряжений на узлах элемента И для точки входа трека 2р группы Gr2P, транзисторы которой выполнены в кармане N-типа проводимости в общей для этих транзисторов области (рис. 2б). На рис. 5а даны зависимости при сигналах на входах A = B = 1, C = 0 с переключением на A = B = C = 0; а на рис. 4б при сигналах на входах элемента A = B = 0

= C = 0 с переключением элемента по входам на A = B = 1, C = 0.

Два семейства зависимостей на рис. 5а и 56 соответствуют трекам через точку входа 2р в область истока РМОП-транзистора Р1.1 в группе Gr2P узла И-НЕ для двух вариантов переключения элемента: из  $1 \to 0$  и из  $0 \to 1$ . Зависимости на рис. 5а характеризуют опережающее переключение элемента И сбором заряда РМОП запертыми транзисторами Р1.1, Р1.2, а зависимости на рис. 56 характеризуют переключение элемента И с дополнительной задержкой при треке с точкой входа 2р в исток открытого РМОП-транзистора Р1.1.

#### Переключение элемента H из $1 \rightarrow 0$ c опережением

Переключившиеся сбором заряда с трека исходно запертые РМОП-транзисторы Р1.1, Р1.2 переводят узел И-НЕ в состояние с напряжением 1 В, что переключает инвертор и выход И через 12 пс после возникновения трека с  $t_{TP} = 100$  пс или 160 пс в состояние логического нуля "0" с напряжением 0.1 В (рис. 5а), что осуществляет опережающее переключение элемента И до смены сигналов на входах элемента при треках с  $t_{TP}$  = = 100 пс и 160 пс. Переключение элемента по входам при  $t_{\Pi EP} = 200$  пс до момента образования трека при  $t_{TP} = 220$  пс вызывает переключение инвертора и запирание РМОП-транзистора инвертора, который после переключения инвертора начинает собирать заряд с трека, что формирует небольшой импульс положительной полярности на выходе элемента И с амплитудой 0.2 В (рис. 5а).

Задержки опережающего переключения элемента И относительно момента образования трека составляют 12 пс при треках как с  $t_{TP}=100$  пс, так и 160 пс. Относительно момента начала переключения входов при  $t_{\Pi EP}=200$  пс задержки опережающего переключения имеют отрицательные значения:  $t_{3Д,\Pi EP}=-88$  пс при  $t_{TP}=100$  пс и  $t_{3Д,\Pi EP}=-28$  пс при  $t_{TP}=160$  пс. При треке с  $t_{TP}=220$  пс переключение происходит с задержкой  $t_{3Д,\Pi EP}=20$  пс относительно изменения входных сигналов при  $t_{\Pi EP}=200$  пс с небольшим импульсом на выходе.

### Переключение элемента H из $0 \to 1$ c дополнительной задержкой

При сигналах на входах A = B = C = 0 РМОП транзисторы P1.1, P1.2 узла И-НЕ открыты и не собирают заряд с трека, так что напряжение на узле И-НЕ и на входе инвертора остается около 1 В. Заряд собирает запертый РМОП-транзистор P1.3 инвертора, что увеличивает напряжение до 0.2 В на выходе И вплоть до переключения элемента И по входам (рис. 5б).

**Рис. 5.** Зависимости напряжений на узлах элемента И мажоритарного элемента при образовании трека с LET =  $60 \text{ M} \cdot \text{B} \times \text{cm}^2/\text{мг}$  с точкой входа 2р в группу транзисторов Gr1P, возникновение трека при  $t_{\text{TP}} = 100 \text{ nc}$ , 160 nc и 220 пс; при  $t_{\text{ПЕР}} = 200 \text{ nc}$  переключение: (а) из A = B = 1, C = 0 в A = B = C = 0; (б) из A = B = C = 0 в A = B = 1, C = 0.

После переключения входов на A = B = 1, C = 0 при  $t_{\Pi EP} = 200$  пс РМОП транзисторы узла И-НЕ запираются, но напряжение на этом узле около 1 В сохраняет заряд на емкости узла. Это сохраняет напряжение на выходе инвертора и выходе И на уровне 0.2 В (рис. 56). Ток открывшихся после переключения NМОП-транзисторов узла И-НЕ (рис. 2a) начинает медленно понижать напряжение на нем. После снижения напряжения и узле И-НЕ ниже 0.5 В начинает переключаться инвертор и повышать напряжение на выходе элемента И.

В итоге зависимости напряжений на узле И-НЕ и выходе И практически повторяются со сдвигом во времени на 60 пс для всех моментов образования треков с  $t_{TP}=100$  пс, 160 пс и 220 пс. Повышенные значения задержек переключения элемента И составляют  $t_{3Д.ПЕР}=224$  пс, 285 пс и 345 пс для треков с  $t_{TP}=100$  пс, 160 пс и 220 пс, что

также повторяет одинаковый сдвиг моментов образования треков по 60 пс.

### 3.3. Сбор заряда с трека NMOП-транзисторами группы Gr2N элемента ИЛИ D2

На рис. 6 приведены зависимости напряжений на узлах элемента ИЛИ для точки входа трека 3 пгруппы Gr2N, транзисторы которой выполнены в кремниевой подложке P-типа проводимости в общей области кремния (рис. 36). На рис. 6а приведены зависимости при сигналах на входах мажоритарного элемента A = B = C = 1 с переключением на A = B = C = 0; а на рис. 6б при сигналах на входах A = B = C = 0 с переключением на A = B = C = 1.

Два семейства зависимостей на рис. 6а и 6б соответствуют трекам через точку входа трека 3n в общую область стоков NMOП-транзисторов узла

**Рис. 6.** Зависимости напряжений на узлах элемента ИЛИ мажоритарного элемента при образовании трека с LET =  $60 \text{ M} \cdot \text{B} \times \text{cm}^2/\text{мг}$  с точкой входа 3n в группу транзисторов Gr2N, образование трека при  $t_{\text{TP}} = 100 \text{ nc}$ , 160 nc и 220 пс; переключение при  $t_{\text{ПFP}} = 200 \text{ nc}$ : (a) из A = B = C = 1 в A = B = C = 0; (б) из A = B = C = 0 в A = B = C = 1.

ИЛИ-НЕ группы Gr2N для вариантов переключения элемента из  $1 \to 0$  и из  $0 \to 1$ . Сбор заряда в момент его образования на треке приводит к переходу NMOП-транзисторов N2.1, N2.2 в инверсное смещение с образованием на узле ИЛИ-НЕ короткого импульса отрицательной полярности с экстремумом -(0.4-0.5) В. Это происходит в обоих случаях исходных сигналов на входах мажоритарного элемента A = B = C = 1 (рис. 6а), так и при A = B = C = 0 (рис. 6б).

Для треков с  $t_{TP} = 100$  пс и 160 пс в первом случае при A = B = C = 1 (рис. 6а) исходно запертый NMOП-транзистор N2.3 инвертора начинает собирать заряд с трека и через 20 пс после образования трека происходит опережающее переключение элемента ИЛИ до изменения сигналов на входах мажоритарного элемента и элемента ИЛИ.

Во втором случае для треков с  $t_{TP} = 100$  пс и 160 пс при A = B = C = 0 (рис. 66) исходно запертый NМОП-транзистор N2.3 инвертора инверсным смещением транзисторов узла ИЛИ-НЕ переключает инвертор и выход ИЛИ до напряжения (0.7-0.73) В, после чего сбор заряда (электронов) с трека запертым NМОП-транзистором N2.3 инвертора переводит выход инвертора и выход ИЛИ в состояние с напряжения 0 В, что образует короткий импульс на выходе ИЛИ сразу после образования трека (рис. 66).

В обоих случаях сигналов на входах через 20 пс после образования треков с  $t_{TP}=100$  пс и 160 пс на выводах NMOП-транзистора N2.3 инвертора устанавливается режим, когда напряжение на его затворе, истоке и стоке близко к 0 B, и в этом состоянии выход ИЛИ удерживается 210-220 пс. При исходных сигналах на входах A=B=C=0 это приводит к дополнительной задержке пере-

**Рис. 7.** Зависимости напряжений на узлах элемента ИЛИ мажоритарного элемента при образовании трека с LET =  $60 \text{ M} \cdot \text{B} \times \text{cm}^2/\text{mr}$  с точкой входа 3р в группу транзисторов Gr2P, возникновение трека при  $t_{\text{TP}} = 100 \text{ nc}$ , 160 nc и 220 пс; при  $t_{\text{ПEP}} = 200 \text{ nc}$  переключение: (a) из A = B = C = 0 в A = B = C = 1; (б) из A = B = C = 1 в A = B = C = 0.

ключения элемента ИЛИ после смены входных сигналов (рис. 6б).

### Переключение элемента ИЛИ из $1 \to 0$ с опережением

После переключения входов на A=B=C=0 в случае треков с  $t_{TP}=100$  пс, 160 пс и 220 пс сохраняется состояние на узле ИЛИ-НЕ и выходе ИЛИ с напряжением 0 В до момента, когда начинает преобладать заряд выходного узла ИЛИ током открытого РМОП-транзистора P2.3 инвертора и напряжение на выходе ИЛИ (рис. 6a) начинает повышаться до уровня 0.8-0.82 В. Затем увеличение напряжения на узле ИЛИ-НЕ переключает инвертор, что формирует импульс помехи с амплитудами 0.8-0.82 В и длительностью 74-77 пс по уровню 0.7 В.

В итоге задержки опережающего переключения элемента ИЛИ относительно момента начала переключения входов при  $t_{\Pi EP} = 200$  пс имеют отрицательные значения:  $t_{3Д,\Pi EP} = -80$  пс при  $t_{TP} = 100$  пс и  $t_{3Д,\Pi EP} = -20$  пс при  $t_{TP} = 160$  пс. При треке с  $t_{TP} = 220$  пс переключение происходит с задержкой  $t_{3Д,\Pi EP} = 40$  пс относительно изменения вхолных сигналов.

### Переключение элемента ИЛИ из $0 \to 1$ с дополнительной задержкой

После состояния с напряжением 0 В на узле ИЛИ-НЕ и выходе ИЛИ в течение 210-220 пс после образования трека при  $t_{TP}=100$  пс, 160 пс и 220 пс (рис. 66) напряжение на выходе ИЛИ до уровня логической единицы "1" начинает повышать заряд емкости выходного узла ИЛИ током

открытого РМОП-транзистора Р2.3 инвертора. В итоге длительности задержек переключения составляют  $t_{\rm 3Д.ПЕР} = 220$  пс, 280 пс и 345 пс по уровню 0.7 В при  $t_{\rm TP} = 100$  пс, 160 пс и 220 пс.

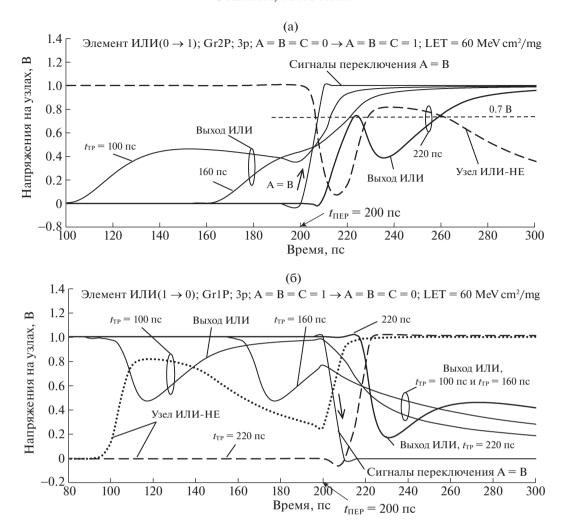

### 3.4. Сбор заряда с трека РМОП-транзисторами группы Gr2P элемента ИЛИ D2

На рис. 7 приведены зависимости напряжений на узлах элемента ИЛИ для точки входа трека 3р группы Gr2P, транзисторы которой выполнены в кремниевом кармане N-типа проводимости в общей для транзисторов области кремния (рис. 36). На рис. 7а приведены зависимости при сигналах на входах A = B = C = 0 с переключением на A = B = C = 1; а на рис. 76 при сигналах на входах A = B = C = 1 с переключением на A = B = C = 0.

Два семейства зависимостей на рис. 7а и 76 соответствуют трекам через точку входа 3р в объединенную область стока транзистора P2.1 и истока P2.2 группы Gr2P для двух вариантов переключения элемента из  $0 \to 1$  и из  $1 \to 0$ . Зависимости на рис. 7а и рис. 7б характеризуют переключение элемента ИЛИ с небольшой задержкой.

При исходных сигналах на входах A=B=C=0 транзисторы P2.1, P2.2 узла ИЛИ-НЕ открыты, PМОП-транзистор P2.3 инвертора собирает заряд (дырки) при образовании треков с  $t_{TP}=100~\text{пc}$ , 160 пс (рис. 7а). Этот сбор увеличивает напряжение на выходе ИЛИ до 0.5 В к моменту переключения входов элемента на A=B=C=1 при  $t_{\Pi EP}=200~\text{nc}$ .

При сигналах на входах A = B = C = 1 (рис. 76) и треке с  $t_{TP} = 100$  пс или 160 пс транзисторы P2.1, P2.2 заперты и с возникновением трека начинают сбор заряда (дырок), что повышает напряжение на узле ИЛИ-НЕ до максимума 0.81 В (см. зависимость на рис. 76 "Узел ИЛИ-НЕ" при  $t_{TP} = 100$  пс). Далее ток открытых транзисторов N2.1, N2.2 снижает напряжение на узле ИЛИ-НЕ до момента переключения входов на A = B = C = 0 при  $t_{ПЕР} = 200$  пс. Напряжение на узле ИЛИ-НЕ отслеживает инвертор, что формирует на выходе ИЛИ до переключения входов импульсы напряжения отрицательной полярности с минимумами напряжения 0.47 В при 117 пс и 177 пс при треках с  $t_{TP} = 100$  пс и 160 пс (рис. 76).

## Переключение элемента ИЛИ из $0 \to 1$ с небольшой задержкой

При переключении входов из A = B = C = 0 на A = B = C = 1 транзисторы P2.1, P2.2 запираются, напряжение на узле ИЛИ-НЕ снижается при  $t_{TP} = 100$  пс и 160 пс, что переключает инвертор и выход элемента ИЛИ без существенной задержки до уровня 1 В (рис. 7а). В случае трека с  $t_{TP} = 220$  пс после смены сигналов на входах напряжение на

узле ИЛИ-НЕ также снижается, но, когда достигает значения 0.07 В (рис. 7а), то сбор заряда с трека запертыми транзисторами Р2.1, Р2.1 начинает поднимать напряжение узла ИЛИ-НЕ до максимума 0.81 В при 237 пс, после чего начинается разряд узла ИЛИ-НЕ током открытых транзисторов N2.1, N2.2 до уровня 0 В. Напряжение на выходе ИЛИ (рис. 7а) отслеживает через инвертор изменение напряжения на узле ИЛИ-НЕ. В итоге на выходе ИЛИ после подъема возникает просадка напряжения, а затем выход ИЛИ достигает 1 В. Длительности задержек переключения составляют  $t_{3Д.\Pi EP} = 12$  пс при  $t_{TP} = 100$  пс,  $t_{3Д.\Pi EP} = 20$  пс при  $t_{TP} = 160$  пс и  $t_{3Д.ПЕР} = 57$  пс при  $t_{TP} = 220$  пс с последующим импульсом "просадки" напряжения длительностью 35 пс до минимального уровня 0.4 В.

Переключение элемента ИЛИ из  $1 \rightarrow 0$  с задержкой

После переключения входов из A=B=C=1 на A=B=C=0 при  $t_{\Pi EP}=200$  пс при треке с  $t_{TP}=100$  пс и 160 пс NМОП-транзисторы узла ИЛИ-НЕ запираются, что быстро увеличивает напряжение на узле до  $1\,B$  (см. зависимость при  $t_{TP}=100$  пс для узла ИЛИ-НЕ на рис. 7б). Инвертор отслеживает это изменение с задержкой, снижая напряжение на выходе ИЛИ до уровня логического нуля. Длительности задержек переключения по уровню  $0.3\,B$  составляют  $t_{3Д.\Pi EP}=40$  пс при  $t_{TP}=100$  пс,  $t_{3Д.\Pi EP}=90$  пс при  $t_{TP}=160$  пс.

В случае образования трека при  $t_{TP}=220$  пс трек образуется после переключения входов при  $t_{\Pi EP}=200$  пс, в этом случае запертые NMOП-транзисторы узла ИЛИ-НЕ после смены сигналов на входах быстро переключают инвертор в состояние с запертым РМОП-транзистором инвертора, напряжение на выходе ИЛИ снижается с 1 В до 0.17 В при t=230 пс (рис. 7б). Затем запертый РМОП-транзистор инвертора, собирая заряд дырок с трека, образует на выходе ИЛИ (рис. 7б) импульс помехи. Длительность задержки переключения при  $t_{TP}=220$  пс составляет  $t_{3Д.\Pi EP}=25$  пс с последующим небольшим импульсом помехи с амплитудным значением 0.46 В и длительностью 95 пс.

Зависимости импульсов напряжения на узле ИЛИ-НЕ и выходе ИЛИ на временных отрезках сигналов, когда на входах A=B=C=0, практически одинаков при  $t\geq 100$  пс на рис. 7а для трека с  $t_{TP}=100$  пс и при  $t\geq 220$  пс на рис. 76 для трека с  $t_{TP}=220$  пс.

### 4. АНАЛИЗ РЕЗУЛЬТАТОВ МОДЕЛИРОВАНИЯ

Зависимости во времени напряжений на выходах элементов И и ИЛИ при образовании им-

**Таблица 1.** Длительности задержек переключения элементов И и ИЛИ  $t_{3Д,\Pi EP}$  на выходах относительно момента переключения элемента входными сигналами при треках с линейным переносом энергии на них 60 МэВ см<sup>2</sup>/мг

| Характер переключения                      | Опережающее<br>переключение элемента |           |          | Переключение элемента<br>с дополнительной задержкой |         |           |         |         |

|--------------------------------------------|--------------------------------------|-----------|----------|-----------------------------------------------------|---------|-----------|---------|---------|

| Переключение входов                        | "0" в "1"                            | "1" в "0" |          | "1" в "0"                                           |         | "0" в "1" |         |         |

| Трек в элемент                             | И                                    | И         | или      | И                                                   | ИЛИ     | И         | или     | ИЛИ     |

| Группа                                     | Gr1N                                 | Gr1P      | Gr2N     | Gr1N                                                | Gr2P    | Gr1P      | Gr2P    | Gr2N    |

| Точка входа трека                          | 2n                                   | 2p        | 3n       | 2n                                                  | 3p      | 2p        | 3p      | 3n      |

| $t_{3Д.\Pi EP}$ , пс при $t_{TP}=100$ пс   | -91 (188)                            | -88       | -80 (74) | 20                                                  | 40      | 224       | 12      | 220     |

| $t_{3Д.\Pi EP}$ , пс при $t_{TP} = 160$ пс | -33 (188)                            | -28       | -20 (75) | 48                                                  | 90      | 285       | 20      | 280     |

| $t_{3Д.\Pi EP}$ , пс при $t_{TP} = 220$ пс | 22 (188)                             | 20        | 40 (77)  | 107                                                 | 25 (95) | 345       | 57 (35) | 345     |

| Графики зависимостей                       | Рис. 4а                              | Рис. 5а   | Рис. 6а  | Рис. 4б                                             | Рис. 7б | Рис. 5б   | Рис. 7а | Рис. 6б |

Примечание: в скобках в таблице указана длительность "просадки" напряжения (импульса помехи), вызванного сбором заряда элемента И и ИЛИ после переключения элемента

пульса помехи под действием сбора заряда с трека одиночной частицы не изменяют свой характер при смене момента образования трека, но смещаются во времени на интервал, равный смещению начала образования трека. В табл. 1 приведены значения задержек переключения элементов И и ИЛИ  $t_{3Д,ПЕР}$  относительно момента переключения входных сигналов для опережающего переключения сбором заряда и с дополнительной задержкой.

При изменении момента образования трека сохраняется практически неизменной зависимость переходного процесса во времени и длительность импульса помехи для конкретных точек входа трека в общую область транзисторов, ограниченную мелкой траншейной изоляцией. В группе опережающих переключений значения времени задержки переключения на выходе элемента даны относительно момента изменения сигналов на входах элемента, в скобках указана длительность "просадки" переключенного уровня (или импульса помехи), вызванной сбором заряда транзисторами элемента после его переключения.

Основные выводы из результатов моделирования следующие:

1. Длительность импульса помехи на выходах элементов И и ИЛИ мажоритарного элемента при переключении по входам элемента и одновременном сборе заряда с трека частицы практически не зависит от момента образования трека для конкретной точки входа трека в область группы транзисторов одного типа проводимости, объединенных в общей области кремния, ограниченной мелкой траншейной изоляцией.

- 2. Транзисторы групп И-НЕ (ИЛИ-НЕ), которые находятся в запертом состоянии при заданных входных сигналах элементов И (ИЛИ), при сборе заряда переключаются, обуславливая опережающее переключение элемента до изменения сигналов на его входах.

- 3. Транзисторы групп И-НЕ (ИЛИ-НЕ), которые находятся в открытом состоянии при заданных входных сигналах элементов И (ИЛИ), не переключаются при сборе заряда ими; при этом их сбор заряда затягивает переключение элемента входными сигналами.

- 4. Длительности импульсов помех максимальны для треков, проходящих через исходно до переключения открытые транзисторы с общими областями их стоков в группе РМОП-транзисторов элемента И и в группе NМОП-транзисторов элемента ИЛИ.

### 5. ЗАКЛЮЧЕНИЕ

Особенности характеристик элементов при сборе заряда с трека ионизирующей частицы совместно с переключением сигналов на входах следует учитывать при проектировании КМОП микропроцессорных систем, предназначенных для космического применения. К этим особенностям относятся практически неизменные длительности нестационарного их состояния независимо от момента возникновения трека, если он возникает до переключения по входам. Другой особенностью является либо опережающее переключение мажоритарного элемента, либо дополнительное увеличение задержки переключения, инициируемые сбором заряда с трека в зависимости от значений сигналов на входах. Задержка переключе-

ния может варьироваться от 12 пс до 345 пс в зависимости от точки входа трека и сигналов на входах.

#### ФИНАНСИРОВАНИЕ

Работа выполнена в рамках госзадания, проект № 0065-2019-0008 "Архитектурные и схемотехнические методы снижения энергопотребления и повышения сбоеустойчивости микропроцессоров и коммуникационных контроллеров высокопроизводительных ЭВМ".

#### СПИСОК ЛИТЕРАТУРЫ

1. Dodd P.E., Shaneyfelt M.R., Felix J.A., Shwank J.R. Production and Propagation of Single-Event Transients in High-Speed Digital Logic ICs // IEEE Transactions on Nuclear Science. 2004. V. 51. № 6. P. 3278—3284.

- 2. *Dodd P.E., Messengill L.W.* Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics // IEEE Transactions on Nuclear Science. 2003, V. 50, № 3, P. 583–602.

- 3. Ferlet-Cavrois V., Messengill L.W., Couker P. Single-Event Transien ts in Digital CMOS A Review // IEEE Transactions on Nuclear Science. 2013. V. 60. № 3. P. 1767–1790.

- 4. Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W. Layout technique for single-event transient mitigation via pulse quenching // IEEE Transactions on Nuclear Science. 2011. V. 58. № 3. P. 885–890.

- 5. *Катунин Ю.В., Стенин В.Я.* Моделирование воздействия одиночных ионизирующих частиц на логические элементы КМОП тройного мажоритарного элемента // Микроэлектроника. 2020. Т. 49. № 3. С. 230—240.

- 6. *Garg R., Khatri S.P.* Analysis and design of resilient VLSI circuits: mitigating soft errors and process variations. New York: Springer, 2010. P. 194–205.

Vestnik Natsional'nogo issledovatel'skogo yadernogo universiteta "MIFI", 2020, vol. 9, no. 4, pp. 345-356

# Features of a Noise Pulse Formation when Switching a CMOS Element and Exposure to an Ionizing Particle

V. Ya. Stenin<sup>a,b,#</sup> and Yu. V. Katunin<sup>a,##</sup>

<sup>a</sup> Scientific Research Institute of System Analysis, Russian Academy of Sciences, Moscow, 117218 Russia

<sup>b</sup> National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Moscow, 115409 Russia

<sup>#</sup>e-mail: vystenin@mephi.ru

##e-mail: katunin@cs.niisi.ras.ru

Received June 18, 2020; revised June 26, 2020; accepted September 8, 2020

**Abstract**—The results of modeling the AND and OR elements as components of the majority element are presented when switching inputs and simultaneously collecting charge from the particle track. The simulation is performed using 3D TCAD physical models of CMOS transistors according to the design rule of 65 nm bulk technology with shallow trench isolation of transistor groups for tracks with linear energy transfer of 60 MeV cm²/mg. It is found that the beginning of switching elements AND and OR at the inputs hardly affects the transient processes of the formation of noise pulses at the output of the element when collecting the charge from the track. The noise pulses are shifted in time by a time interval equal to the time offset of the track relative to the time of switching element inputs. Collection of the charge from the track leads either to switching an element in advance of the input signals changing or to an additional switching delay. The widths of the noise pulses at the outputs of the AND and OR elements are distributed in the range from 12 to 345 ps. At the same time, the duration of the noise pulse remains almost unchanged for the each specific track input point into the common area of the transistor location regardless of the time of formation of the track.

Keywords: noise pulse, logical element, simulation, single particle, charge collection, track

DOI: 10.1134/S2304487X20030098

#### **REFERENCES**

1. Dodd P.E., Shaneyfelt M.R., Felix J.A., Shwank J.R., Production and propagation of single-event tran-

sients in high-speed digital logic ICs, *IEEE Transactions on Nuclear Science*, 2004, vol. 51, no. 6, pp. 3278—3284.

- 2. Dodd P.E., Messengill L.W., Basic mechanisms and modeling of single-event upset in digital microelectronics, *IEEE Transactions on Nuclear Science*, 2003, vol. 50, no. 3, pp. 583–602.

- 3. Ferlet-Cavrois V., Messengill L.W., Couker P., Single-event transients in digital CMOS A review, IEEE Transactions on Nuclear Science, 2013, vol. 60, no. 3, pp. 1767–1790.

- 4. Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W., Layout technique

- for single-event transient mitigation via pulse quenching, *IEEE Transactions on Nuclear Science*, 2011, vol. 58, no. 3, pp. 885–890.

- 5. Katunin Yu.V., Stenin V.Ya., Modeling of single ionizing particles impact on logic elements of a CMOS triple majority gate, *Russian Microelectronics*, 2020, vol. 49, no. 3, pp. 214–223.

- 6. Garg R., Khatri S.P., *Analysis and design of resilient VLSI circuits: Mitigating soft errors and process variations*. New York: Springer, 2010, pp. 194–205.