## \_\_ ПРИКЛАДНАЯ МАТЕМАТИКА \_\_\_\_\_\_ И ИНФОРМАТИКА

УЛК 621.382+621.396.6

# ОСОБЕННОСТИ ОБРАЗОВАНИЯ ИМПУЛЬСОВ ОШИБОК НА ВЫХОДЕ КМОП ТРОЙНОГО МАЖОРИТАРНОГО ЭЛЕМЕНТА НА ЛОГИКЕ И-НЕ ПРИ СБОРЕ ЗАРЯДА С ТРЕКОВ ОДИНОЧНЫХ ИОНИЗИРУЮШИХ ЧАСТИЦ

© 2021 г. В. Я. Стенин<sup>1,2,\*</sup>, Ю. В. Катунин<sup>2,\*\*</sup>

<sup>1</sup>Национальный исследовательский ядерный университет "МИФИ", Москва, 115409, Россия <sup>2</sup>НИИ системных исследований Российской академии наук, Москва, 117218, Россия \*e-mail: vvstenin@mephi.ru

\*\*e-mail: katunin@cs.niisi.ras.ru

Поступила в редакцию 13.05.2021 г.

После доработки 14.05.2021 г.

Принята к публикации 25.05.2021 г.

В работе исследуется 65-нм объемный КМОП тройной мажоритарный элемент на логике И-НЕ с топологической структурой, в которой все транзисторы выходного ЗИ-НЕ элемента по одному введены в группы транзисторов того же типа трех входных 2И-НЕ элементов, взаимно отделенных мелкой траншейной изоляцией. Особенностью исследования является классификация и анализ импульсов ошибок, возникающие на выходе мажоритарного элемента при сборе заряда с треков одиночных ионизирующих частиц как до, так и после переключения элемента по входам. Исследование проводится средствами 3D TCAD с использованием треков с нормальным направлением к поверхности чипа и линейной передаче энергии частицей на трек 60 MэВ × см<sup>2</sup>/мг. Установлены четыре вида импульсов ошибок, образующихся на выходе мажоритарного элемента, которые основаны на переходе элемента в нестационарное состояние при сборе заряда с треков одиночных частии. Это лва вила импульсов оппибки, образующихся до переключения элемента по входам их состояния "0" в состояние "1": импульс с длительностью нестационарного состояния, если момент времени образования трека ближе к моменту переключения сигналов на входах из состояния "0" в "1" по сравнению с длительностью нестационарного состояния, и импульс опережающего переключения элемента до переключения входов. Кроме того, два вида импульсов ошибки, образующихся после переключения элемента по входам их состояния "1" в состояние "0", а именно импульс ошибки с дополнительной задержкой переключения элемента и импульс ошибки с длительностью нестационарного состояния после переключения элемента.

*Ключевые слова:* импульс ошибки, логический элемент, мажоритарный элемент, моделирование, одиночная частица, сбор заряда, трек

**DOI:** 10.1134/S2304487X21030123

### 1. ВВЕДЕНИЕ

Длительность импульса ошибки на выходе логического комбинационного элемента зависит от длительности его нестационарного состояния, которое зависит от энергии, переданной частицей на трек, от сочетания логических уровней сигналов на входах элемента [1, 2]. Интересным результатом 3D моделирования, представленным впервые в работе [2], был эффект перехода NMOП-транзисторов КМОП-инвертора с проектной нормой 0.18 мкм по объемной технологии в инверсный режим смещения при сборе заряда с треков с линейной передачей энергии на них более 3 МэВ×см²/мг с достижением инверсного смещения на стоке менее -0.7 В, что характерно в

настоящее время при образовании импульсов ошибок во всех КМОП мажоритарных элементах при сборе заряда с трека NМОП-транзисторами.

Установлены количественные параметры процессов образования импульсов ошибок на выходах КМОП мажоритарного элемента на основе трех двухвходовых КМОП логических элементов И и двух двухвходовых ИЛИ с проектной нормой 65-нм КМОП объемный технологии [3] с шириной каналов транзисторов 400 нм, также мажоритарного элемента на основе трех КМОП двухвходовых логических элементов И с шириной каналов транзисторов 400 нм и одного трехвходного элемента ИЛИ с шириной каналов транзисторов 800 нм [4]. Установлено, что начало переключе-

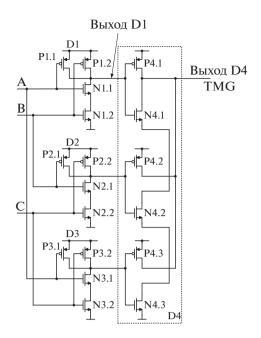

**Рис. 1.** Схема КМОП тройного мажоритарного элемента на И-НЕ логических элементах.

ния элементов И и ИЛИ по входам практически не влияет [3] на зависимость переходных процессов образования импульсов помех на выходах мажоритарных элементов. Задержки переключения мажоритарного элемента заключены в пределах от 12 пс [3] и 9 пс [4] при опережающем переключении сбором заряда с трека до 345 пс [3] и 600 пс [4] при переключении с дополнительной задержкой.

При треках, возникающих после переключения элемента по входам, происходит образование импульса помехи на выходе элемента с длительностью того нестационарного состояния, которое характерно для данной точки входа трека [4].

Предложено использовать [5] вместо глобальных цепей тактирования асимметричное групповое троированное тактирование, приводящее к повышению помехоустойчивости и снижению энергопотребления цепями тактирования. При этом цепи тактирования синхронных триггерных резервируемых устройств объединяются на входах тройных мажоритарных элементов. При этом обязательно должно учитываться возможное возникновение импульсов ошибок на выходе мажоритарного элемента при использовании под воздействием одиночных ионизирующих частиц. Интересным направлением работ, обоснованных в [6] для повышения сбоеустойчивости комбинационной логики, является использование тройного триггерного элемента на пяти КМОП простейших триггерах-защелках для замены двухкаскадных синхронных троированных триггеров, которые пропускали собственные сбои при пере-

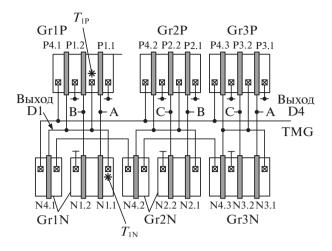

**Рис. 2.** Эскиз топологии, входы элемента обозначены как A, B, C, а выход как "Выход D4/TMG".

даче сигналов на входы мажоритарного элемента. Однако требуется серьезная практическая проверка реального выигрыша в сбоеустойчивости.

Целью данной работы является исследование КМОП тройного мажоритарного элемента тройного мажоритарного элемента (triple majority gate — TMG) на основе трех двухвходовых КМОП-элементов 2И-НЕ и одного трехвходового 3И-НЕ с шириной каналов всех транзисторов 400 нм. Данный элемент содержит 18 транзисторов и характеризуется относительно малой чувствительностью к воздействиям одиночных частиц [7].

## 2. СХЕМА И КОНСТРУКЦИЯ МАЖОРИТАРНОГО ЭЛЕМЕНТА

Объектом 3D TCAD физического моделирования является тройной мажоритарный элемент на логике И-НЕ, содержащий 18 транзисторов, схема которого представлена на рис. 1. Элемент имеет оригинальную топологию объединения двух РМОП-транзисторов каждого из трех входных элементов 2И-НЕ и одного РМОП-транзистора выходного элемента 3И-НЕ как отдельные группы РМОП-транзисторов Gr1P-Gr3P (рис. 2), каждая в своей области кремния (рис. 2), окруженной неглубокой траншейной изоляцией.

Эффект разделения заряда между соседними транзисторами в общей области используется для коррекции импульса ошибки [8]. Такую же конструкцию имеет группа NMOП-транзисторов Gr3N, а группы Gr1N, Gr2N выполнены с отдельными областями кремния для NMOП-транзисторов N4.1 и N4.2 элемента D4 (рис. 2), что обусловлено особенностями электрических связей NMOП-транзисторов элемента D4 в отличие от РМОП-транзисторов.

Использованная компоновка транзисторов в группы — по два из входных 2И-НЕ элементов и одного из 3И-НЕ элемента обеспечила одинаковость образования выходного сигнала мажоритарного элемента при сборе заряда с треков с точками входа в группы РМОП-транзисторов Gr1P-Gr3P (рис. 2), а также практически одинаковое образование импульсов ошибок на сбор заряда с треков в группах NМОП-транзисторов Gr1N-Gr3N. Это позволило описать реакцию мажоритарного элемента меньшим количеством зависимостей.

Ширина всех транзисторов составляет 400 нм. Используются два трека: трек  $T_{1N}$  для группы NMOП-транзисторов Gr1N и трек  $T_{1P}$  для группы PMOП-транзисторов. Точки входа треков с линейной передачей на трек 60 MэВ×см²/мг и с направлениями по нормали к поверхности кристалла отмечены звездочками на рис. 2. 3D TCAD физическая модель мажоритарного элемента, использованная для моделирования, основана на физических моделях КМОП-транзисторов, представленных в работе [9]. Результаты исследования получены путем моделирования с использованием симулятора Sentaurus при температуре 25°С и напряжении питания 1.0 В.

В тексте используется сокращенное обозначение тройного мажоритарного элемента как TMG (triple majority gate).

### 3. МЕТОДИКА МОДЕЛИРОВАНИЯ

Рассматриваются четыре варианта возникновения ложных сигналов на выходе TMG.

- 1) Трек образуется до переключения ТМG по входам из состояния "0" в состояние "1" и импульс ошибки образуется и оканчивается до переключения ТМG по входам из состояния "0" в "1".

- 2) Происходит опережающее переключение TMG сбором заряда с трека до переключения (смены) сигналов на входах TMG из состояния "0" в состояние "1".

- 3) Трек образуется до переключения ТМG по входам из состояния "1" в состояние "0" и образуется дополнительная задержка переключения ТМG в состояние "0".

- 4) Трек образуется после переключения ТМG по входам из состояния "1" в состояние "0" и возникает на выходе ТМG импульс помехи положительной полярности. Во всех случаях длительность нестационарного состояния одинакова при одинаковых параметрах трека, включая точку входа трека, и те же сочетания сигналов на входах ТМG.

Используются два вида треков: трек  $T_{\rm 1N}$  с точкой входа в область NMOП-транзисторов и трек  $T_{\rm 1P}$  с точкой входа в область PMOП-транзисторов с направлением по нормали к поверхности кристалла и линейной передачей энергии на трек

60 МэВ  $\times$  см²/мг. Использованы следующие моменты времени образования треков: 1) треки с  $t_{\rm TP}=100$  пс и  $t_{\rm TP}=300$  пс и 400 пс в случае переключения ТМG при  $t_{\rm ПЕР}=600$  пс по входам из состояния "0" в состояние "1"; 2) треки с  $t_{\rm TP}=1.1$  нс и  $t_{\rm TP}=1.28$  нс в случае переключения ТМG при  $t_{\rm ПЕР}=1.2$  нс по входам из состояния "1" в состояние "0". Длительность переходного процесса при сборе заряда с трека частицы, определяемого как single event transients — SET, обозначается как  $t_{\rm SET}$ .

### 4. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ

### 4.1. Сбор заряда NMOП-транзисторами

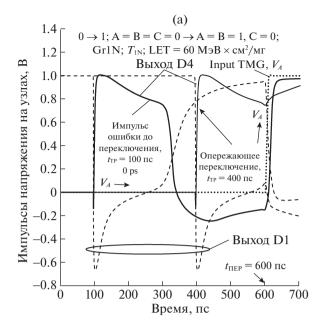

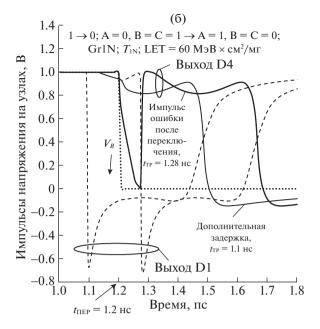

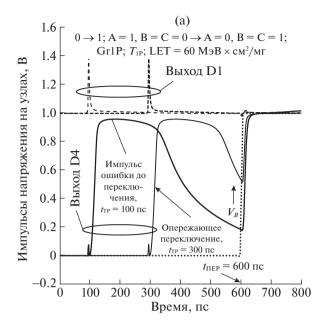

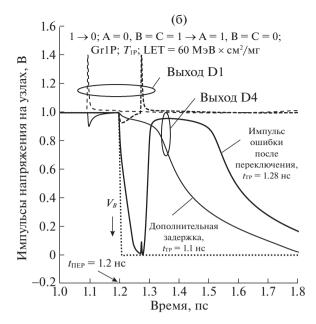

4.1.1. Переключение входов мажоритарного элемента из A = B = C = 0 в A = B = 1, C = 0 и из A = B = 1. C = 0 в A = B = C = 0. На рис. 3 приведены импульсы напряжений на выходах элементов D1 и D4 мажоритарного элемента при его переключении по входам A, B, C и сборе заряда с трека с LET =  $= 60 \text{ M} \rightarrow \text{B} \times \text{см}^2/\text{мг}$ , точка входа трека  $T_{1N}$  в группу Gr1N. Переключение по входам из "0" в "1" при  $t_{\Pi EP}=600$  пс из A=B=C=0 в A=B=1, C=0, образование трека при  $t_{\rm TP}=100$  пс и 400 пс. Переключение по входам из "1" в "0" при  $t_{\rm ПЕР}=1.2$  нс из A = B = 1, C = 0 в A = B = C = 0, образование трека при  $t_{\rm TP} = 1.16$  нс и 1.28 пс. Стрелки с обозначением  $V_{\rm A}$  показывают направление переключения входов A = B и выхода мажоритарного элемента из состояния из "0" в "1" (рис. За) и из "1" в "0" (рис. 3б). Жирными линиями на рис. 3 отмечены импульсы с длительностью нестационарного состояния.

Сбор заряда с трека  $T_{1N}$  одиночной частицы в зависимости от момента образования трека относительно момента переключения мажоритарного элемента по входам вызывает четыре вида импульсов ошибки на выходе TMG (выход D4). Это импульс ошибки с длительностью нестационарного состояния 220 пс до переключения ТМС по входам, импульс ошибки опережающего переключения ТМС перед переключением ТМС на входах с "0" на "1" (рис. 3а), а также импульс ошибки с дополнительной задержкой и импульс ошибки после переключения ТМG по входам с "1" на "0" (рис. 3б). Когда трек  $T_{1N}$  формируется при  $t_{\rm TP} = 100$  пс или  $t_{\rm TP} = 400$  пс (рис. 3a), транзисторы N1.1, N1.2 (закрыты в начале сбора, а после изменения А, В, С открыты) начинают сбор заряда, который сразу переводит транзисторы N1.1, N1.2 в режим инверсного смещения ("0"). Это упреждающе переключает выход D4 в состояние "1" перед изменением сигналов на входах TMG. Если длительность нестационарного состояния TMG при сборе заряда меньше интервала времени от момента формирования трека  $T_{1N}$  до момента начала переключения входов А, В, С, то это

**Рис. 3.** Импульсы напряжений на выходах элементов D1 и D4 мажоритарного элемента при переключении и сборе заряда с трека с LET =  $60~{\rm M} \cdot {\rm B} \cdot {\rm cm}^2/{\rm Mr}$ , точка входа трека  $T_{1N}$  в группу Gr1N: (а) переключение по входам при  $t_{\Pi \rm EP}$  =  $600~{\rm nc}$  из A = B = C = 0 в A = B = 1, C = 0, образование трека при  $t_{\rm TP}$  =  $100~{\rm nc}$  и 400 пс; (б) переключение по входам при  $t_{\Pi \rm EP}$  =  $1.2~{\rm nc}$  из A = B = 1, C = 0 в A = B = C = 0, образование трека при  $t_{\rm TP}$  =  $1.16~{\rm nc}$  и  $1.28~{\rm nc}$ .

приводит к формированию опережающего переключения ТМG импульсом ошибки (рис. 3а, трек с  $t_{\rm TP}=400$  пс). Импульсы ошибки после переключения входов A, B, C при  $t_{\rm ПЕР}=1.2$  нс, приведены на рис. 3б. Сбор заряда с трека с  $t_{\rm TP}=1.16$  нс формирует дополнительную задержку переключения на выходе ТМG (выход D4). Сбор заряда с трека  $t_{\rm TP}=1.28$  нс генерирует импульс ошибки на выходе ТМG с длительностью нестационарного состояния, как и на рис. 3а, с той же длительностью нестационарного состояния 220 пс.

**4.1.2.** Переключение входов мажоритарного элемента из A=1, B=C=0 в A=0, B=C=1 и из A=0, B=C=1 в A=1, B=C=0. На рис. 4 приведены импульсы напряжений на выходах элементов D1 и D4 мажоритарного элемента при его переключении по входам A, B, C и сборе заряда с трека с LET = 60 M в  $\times$  см²/мг, точка входа трека  $T_{1N}$  в группу Gr1N. Жирными линиями на рис. 4 отмечены импульсы с длительностью нестационарного состояния.

На рис. 4а импульсы ошибок привязаны к моменту начала переключения элемента по входам из "0" в "1" при  $t_{\Pi EP}=600$  пс, когда сочетание входных сигналов A=1, B=C=0 меняется на A=0, B=C=1. Образование трека при  $t_{TP}=100$  пс приводит к импульсу ошибки с длительностью неста-

ционарного состояния, а при  $t_{\rm TP}=300$  пс к импульсу опережающего переключения ТМG сбором заряда с трека (рис. 4а). На рис. 46 переключение по входам происходит из "1" в "0" при  $t_{\rm ПЕР}=1.2$  нс с сменой A=0, B=C=1 на A=1, B=C=0. Образование трека при  $t_{\rm TP}=1.1$  нс приводит к импульсу ошибки с дополнительной задержкой, а при  $t_{\rm TP}=1.28$  нс к импульсу ошибки с длительностью нестационарного состояния 380 пс. Стрелки с обозначением  $V_{\rm B}$  дают направление переключения входов B=C элемента D2 и выхода мажоритарного элемента из состояния из "0" в "1" (рис. 4а) и из "1" в "0" (рис. 4б).

На рис. 4 даны результаты моделирования импульсов ошибки с треком  $T_{1N}$  с  $t_{TP} = 100$  пс и  $t_{TP} = 300$  пс, но с другими комбинациями уровней логических сигналов на входах A, B, C, чем приведенные на рис. 3. В случае формирования импульсов ошибок на рис. 4 коммутацией входов ТМG управляет элемент D2, а не D1, как на рис. 3. В результате на рис. 4 мы имеем увеличение длительности нестационарного состояния ТМG почти в два раза (до 380 пс) по сравнению с импульсами, приведенными на рис. 3. В этом случае после начала сбора заряда и перехода транзисторов N1.1, N1.2 в режим инверсного смещения ("0") зарядку емкости узла D1 производит только один открытый РМОП-транзистор P1.2 (P1.1 закрыт

**Рис. 4.** Импульсы напряжений на выходах элементов D1 и D4 мажоритарного элемента при переключении и сборе заряда с трека с LET =  $60~{\rm MpB\cdot cm}^2/{\rm Mr}$ , точка входа трека  $T_{\rm 1N}$  в группу Gr1N: (а) переключение по входам при  $t_{\rm ПEP}$  =  $600~{\rm nc}$  из A = 1, B = C = 0 в A = 0, B = C = 1, образование трека при  $t_{\rm TP}$  =  $100~{\rm nc}$  и  $300~{\rm nc}$ ; (б) переключение по входам при  $t_{\rm ПEP}$  =  $1.2~{\rm hc}$  из A = 0, B = C = 1 в A = 1, B = C = 0, образование трека при  $t_{\rm TP}$  =  $1.1~{\rm hc}$  и  $1.28~{\rm hc}$ .

при  $A=1,\ B=0$ ), тогда как в случае импульсов ошибки на рис. 3 это выполняли два открытых транзистора P1.1 и P1.2, заряжая емкость узла D1. Соответственно, длительности всех вариантов импульсов ошибки в данном случае имеют большие значения по сравнению с импульсами на рис. 3.

4.2. Сбор заряда РМОП-транзисторами. Переключение входов мажоритарного элемента из

$$A=1$$

,  $B=C=0$  в  $A=0$ ,  $B=C=1$  и из  $A=0$ ,  $B=C=1$  в  $A=1$ ,  $B=C=0$

На рис. 5 приведены импульсы напряжений на выходах элементов D1 и D4 мажоритарного элемента при его переключении по входам А, В, С и сборе заряда с трека с LET =  $60 \text{ M} \cdot \text{B} \times \text{cm}^2 / \text{мг}$ , точка входа трека  $T_{1P}$  в группу Gr1P. На рис. 5а переключение по входам из "0" в "1" (из A = 1, B = C = 0 $_{\rm B}$  A = 0, B = C = 1) происходит при  $t_{\rm \Pi EP}$  = 600 пс с образование треков при  $t_{TP} = 100$  пс и 300 пс. На рис. 5б переключение по входам из "1" в "0" (из A = 0, B = C = 1 в A = 1, B = C = 0) происходит при  $t_{\text{ПЕР}} = 1.2 \text{ нс с образованием треков при } t_{\text{ТР}} = 1.1 \text{ нс}$ и 1.28 нс. Стрелки с обозначением  $V_{\rm B}$  показывают направление переключения входов В = С элемента D2 и выхода мажоритарного элемента из состояния из "0" в "1" (рис. 5а) и из "1" в "0" (рис. 5б). Жирными линиями на рис. 5 отмечены импульсы

ошибок с длительностью нестационарного состояния.

При заданных входных сигналах до переключения из "0" в "1" транзисторы P1.1, P1.2 группы Gr1P элемента D1 открыты, а транзистор P4.1 той же группы, но элемента D4 заперт. Сбор заряда запертым транзистором P4.1 с трека  $T_{\rm 1P}$  с точкой входа в группу Gr1P опережающе до смены сигналов на входах A, B, C переключает выход D4 в состояние "1". В начале сбора заряда как при треке с  $t_{\rm TP} = 100$  пс, так и с  $t_{\rm TP} = 300$  пс транзисторы P1.1, P1.2 кратковременно (длительность около 10 пс, напряжение 1.4 В) переходят в инверсное смещение.

На рис. 5 приведены два импульса ошибки с длительностью нестационарного состояния до (рис. 5а) и после (рис. 5б) переключения ТМG по входам, импульс ошибки опережающего переключения ТМG перед переключением входов ТМG с "0" на "1" (рис. 5а) и импульс ошибки с дополнительной задержкой после переключения с "1" на "0" (рис. 5б). Собирая заряд с трека, транзистор Р4.1 поддерживает напряжение плоских вершин импульсов ошибки около 0.95 В. После завершения сбора заряда небольшой ток цепочки трех транзисторов N4.1-N4.3 элемента D4 начинает разряжать емкость узла D4 до уровня логического нуля "0", чем завершается формирование

**Рис. 5.** Импульсы напряжений на выходах элементов D1 и D4 мажоритарного элемента при переключении и сборе заряда с трека с LET =  $60~{\rm MpB\cdot cm^2/mr}$ , точка входа трека  $T_{\rm 1P}$  в группу Gr1P: (а) переключение по входам при  $t_{\rm ПEP}$  =  $600~{\rm nc}$  из A = 1, B = C = 0 в A = 0, B = C = 1, образование трека при  $t_{\rm TP}$  =  $100~{\rm nc}$  и 300 пс; (б) переключение по входам при  $t_{\rm ПEP}$  =  $1.2~{\rm nc}$  из A = 0, B = C = 1 в A = 1, B = C = 0, образование трека при  $t_{\rm TP}$  =  $1.1~{\rm nc}$  и  $1.28~{\rm nc}$ .

импульсов ошибки. Длительность нестационарного состояния по уровню 0.5 В составляет 295 пс.

# 5. ВЫВОДЫ ПО РЕЗУЛЬТАТАМ МОДЕЛИРОВАНИЯ

Формальные результаты моделирования импульсов ошибок (ложных выходных сигналов мажоритарного элемента) приведены в таблице. В таблице 1 даны значения длительностей импульсов ошибок ( $t_{\rm ИМП.ОШИБ}$ , пс) на выходе мажоритарного элемента для четырех видов ошибок. Сбор заряда с трека частицы моделировался при линейной передаче энергии частицей на трек  $60 \text{ M} \rightarrow \text{B} \times \text{cm}^2/\text{м} \Gamma$  и точках входа трека в область NMOП-транзисторов Gr1N, а также в область РМОП-транзисторов Gr1P для двух вариантов переключения сигналов на входах элемента и для всех приведенных значений моментов образования треков. Значения вариантов импульсов ошибок  $t_{\text{ИМП,ОШИБ}}$  лежат в диапазоне от 210 пс до 380 пс. Конкретные значения логических уровней сигналов на входах А, В, С приведены на рисунках и подрисуночных подписях, на которые даны ссылки в табл.

Все варианты импульсов ошибок (помех) имеют положительную полярность, то есть соответствуют логическим единицам "1", образующимся на выходе мажоритарного элемента только при

его исходном состоянии в логическом нуле "0". Это либо импульсы ошибок с длительностью нахождения мажоритарного элемента в нестационарном состоянии, образующиеся либо до переключения элемента из состояния "0" в "1", либо после переключения элемента из состояния "1" в "0". А также это импульсы ошибок при досрочном (опережающем) переключении выхода мажоритарного элемента из состояния "0" в "1" в самый начальный этап сбора заряда с трека частицы, либо при образовании дополнительной задержки переключения выхода элемента в состояние "0", находящегося до этого в состоянии "1".

Изложенные положения справедливы при сборе заряда как NMOП-, так и РМОП-транзисторами с треков одиночных частиц, с точками входа в их общие области кремния, объединяющие по два транзистора из 2И-НЕ элементов D1-D3 с одним транзистором из 3И-НЕ элемента D4.

### ЗАКЛЮЧЕНИЕ

Надежность наноэлектронных вычислительных систем с резервированием, предназначенных для космических применений, зависит от устойчивости мажоритарной логики к воздействию одиночных ионизирующих частиц. Результатом

**Таблица 1.** Значения длительностей импульсов ошибок ( $t_{\rm ИМП.ОШИБ}$ , пс) на выходе мажоритарного элемента, образующихся при сборе заряда с трека частицы при линейной передаче энергии на трек 60 МэВ  $\times$  см<sup>2</sup>/мг в зависимости от точки входа трека и момента его образования

| Характер<br>импульсов<br>ошибок       | Импульсы ошибок до переключения элемента из состояния "0" в "1" |          |                                             |          | Импульсы ошибок после переключения элемента из состояния "1" в "0" |                   |                                                           |                   |

|---------------------------------------|-----------------------------------------------------------------|----------|---------------------------------------------|----------|--------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-------------------|

| Варианты<br>импульсов<br>ошибок       | Импульсы ошибок с длительностью нестационарного состояния       |          | Опережающее<br>переключение<br>элемента ТМG |          | Переключение элемента ТМС с дополнительной задержкой               |                   | Импульсы ошибок с длительностью нестационарного состояния |                   |

| Трек в группу                         | Gr1N                                                            | Gr1P     | Gr1N                                        | Gr1P     | Gr1N                                                               | Gr1P              | Gr1N                                                      | Gr1P              |

| Трек                                  | $T_{1 m N}$                                                     | $T_{1P}$ | $T_{1 m N}$                                 | $T_{1P}$ | $T_{1 m N}$                                                        | $T_{1\mathrm{P}}$ | $T_{1 m N}$                                               | $T_{1\mathrm{P}}$ |

| <i>t</i> <sub>ТР</sub> , пс<br>100 пс | 100 пс                                                          | 100 пс   | 400 пс/<br>300 пс                           | 300 пс   | 1.16 нс/<br>1.1 нс                                                 | 1.1 нс            | 1.28 нс                                                   | 1.28 нс           |

| $t_{\rm ИМП.ОШИБ}$ , пс               | 220/<br>380                                                     | 295      | 200*/<br>300*                               | 300*     | 180**/<br>290**                                                    | 210**             | 220/<br>380                                               | 295               |

| Рисунок                               | Рис. 3а/<br>Рис. 4а                                             | Рис. 5а  | Рис. 3а/<br>Рис. 4а                         | Рис. 5а  | Рис. 3б/<br>Рис. 4б                                                | Рис. 5б           | Рис. 3б/<br>Рис. 4б                                       | Рис. 56           |

Примечание: значком \* отмечены длительности опережения переключения; значком \*\* отмечены длительности переключения с дополнительной задержкой относительно смены сигналов на входах мажоритарного элемента.

моделирования мажоритарного элемента на КМОП-логике И-НЕ на 18 транзисторах с оригинальной топологической структурой является установление четырех видов импульсов ошибок, образующихся на выходе мажоритарного элемента, которые основаны на переходе элемента в нестационарное состояние при сборе заряда с треков одиночных частиц. Эти импульсы ошибок включают два вида импульсов, образующихся до переключения элемента по входам их состояния "0" в состояние "1", а именно, импульс с длительностью нестационарного состояния, и импульс опережающего переключения элемента до переключения входов. Кроме того, есть два вида импульсов ошибки, образующихся после переключения элемента по входам их состояния "1" в состояние "0", а именно импульс ошибки с дополнительной задержкой переключения элемента и импульс ошибки с длительностью нестационарного состояния после переключения элемента. Возникающие временные сдвиги ложной смены выходного сигнала мажоритарного элемента следует учитывать при проектировании высокопроизводительных быстродействующих вычислительных систем, предназначенных для космического применения.

### БЛАГОДАРНОСТИ

Исследование выполнено при финансовой поддержке РФФИ в рамках научного проекта № 19-07-00651.

### СПИСОК ЛИТЕРАТУРЫ

- 1. *Dodd P.E., Massengill L.W.* Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics // IEEE Transactions on Nuclear Science. 2003. V. 50. № 3. P. 583–602.

- 2. *Dodd P.E., Shaneyfelt M.R., Felix J.A., Shwank J.R.* Production and Propagation of Single-Event Transients in High-Speed Digital Logic ICs // IEEE Transactions on Nuclear Science. 2004. V. 51. № 6. P. 3278—3284.

- 3. *Стенин В.Я., Катунин Ю.В.* Особенности образования помех при переключении КМОП-элемента и воздействии ионизирующей частицы // Вестник НИЯУ МИФИ. 2020. Т. 9. № 4. С. 345—356.

- 4. *Стенин В.Я., Катунин Ю.В.* Моделирование переходных процессов в мажоритарном элементе при переключении и сборе заряда с трека одиночной частицы // Микроэлектроника. 2020. Т. 49. № 5. С. 353—365.

- 5. Schrape O., Breitenreiter A., Andjelkovic M., Krstic M. D-SET Mitigation Using Common Clock Tree Inser-

- tion Techniques for Triple-Clock TMR Flip-Flop // in 21st Euromicro Conference on Digital System Design (DSD), 2018, P. 201–205.

- 6. *Jianwei Zhang, Yajun Li, Tao Han, Jinghu Li*. Radiation Hardened Design Based on TMR-5DFF for ASIC // in IEEE 5th International Conference on Computer and Communications (ICCC). 2019. P. 981–986.

- 7. Danilov I.A., Gorbunov M.S., Antonov A.A. SET Tolerance of 65 nm CMOS Majority Voters: A Comparative

- Study // IEEE Transactions on Nuclear Science. 2014. V. 61. P. 1597–1602.

- 8. Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W. Layout technique for single-event transient mitigation via pulse quenching // IEEE Transactions on Nuclear Science. 2011. V. 58. № 6. 3. P. 885–890.

- 9. *Garg R., Khatri S.P.* Analysis and design of resilient VLSI circuits: mitigating soft errors and process variations. New York: Springer, 2010. pp. 194–205.

Vestnik Natsional'nogo issledovatel'skogo vadernogo universiteta "MIFI", 2021, vol. 10, no. 3, pp. 244–252

# Logic when Collecting a Charge from Tracks of Single Ionizing Particles

V. Ya. Stenin<sup>a,b,#</sup> and Yu. V. Katunin<sup>b,##</sup>

<sup>a</sup> National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Moscow, 115409 Russia

<sup>b</sup> Scientific Research Institute of System Analysis, Russian Academy of Sciences, Moscow, 117218 Russia

<sup>#</sup>e-mail: vvstenin@mephi.ru

##e-mail: katunin@cs.niisi.ras.ru

Received May 13, 2021; revised May 14, 2021; accepted May 25, 2021

Abstract—We have studied a 65-nm bulk CMOS triple majority gate based on the NAND logic with a topological structure in which all the transistors of the output 3NAND gate are one-by-one inserted into groups of transistors of the same type of three input NAND gates mutually separated by shallow trench insulation. The study involves the classification and analysis of error pulses that occur at the output of the majority gate when collecting charge from tracks of single ionizing particles both before and after switching the element at the inputs. The study carried out by means of 3D TCAD using tracks with a normal direction to the chip surface and a linear energy transfer of 60 MeV cm<sup>2</sup>/mg by a particle to a track. Four types of error pulses formed at the output of the majority element are established, which are based on the transition of the element to a nonstationary state when collecting charge from tracks of single particles. These are two types of error pulses formed before switching the element at the inputs of their 0 state to the 1 state. These is an error pulse with the nonstationary state duration, when the duration from the time of the track formation is farther to the time of switching the signals at the inputs from the 0 state to the 1 state compared to the duration of the nonstationary state, and an error pulse of ahead switching of the element before switching the inputs. In addition, there are two more types of error pulses generated at the output of the majority element after switching the inputs from the 1 state to the 0 state, namely, an error pulse with an additional delay in switching the element and an error pulse with the duration of the nonstationary state after switching the element.

Keywords: error pulse, logical element, triple majority gate, simulation, single particle, charge collection, track

DOI: 10.1134/S2304487X21030123

### **REFERENCES**

- 1. Dodd P.E., Messengill L.W., Basic mechanisms and modeling of single-event upset in digital microelectronics // *IEEE Transactions on Nuclear Science*, 2003, vol. 50, no. 3, pp. 583–602.

- Dodd P.E., Shaneyfelt M.R., Felix J.A., Shwank J.R., Production and Propagation of Single-Event Transients in High-Speed Digital Logic ICs, *IEEE Transac*-

- tions on Nuclear Science, 2004, vol. 51, no. 6, pp. 3278-3284

- Stenin V.Ya., Katunin Yu.V., Osobennosti obrazovaniya impul'sov oshibok na vyhode CMOS trojnogo mazhoritarnogo elementa na logike NAND pri sbore zaryada s trekov odinochnyh ioniziruyushchih chastic (Features of a noise pulse formation when switching a CMOS element and exposure to an ionizing particle), Vestnik NIYaU MIFI, 2020, vol. 9, no. 4, pp. 345–356.

- 4. Stenin V.Ya, Katunin Yu.V., Simulation of transients in a majority element upon switching and collecting charge from the track of a single particle, *Russian Microelectronics*, 2020, vol. 49, no. 5, pp. 332–344.

- Schrape O., Breitenreiter A., Andjelkovic M., Krstic M., D-SET Mitigation Using Common Clock Tree Insertion Techniques for Triple-Clock TMR Flip-Flop, 21st Euromicro Conference on Digital System Design (DSD), 2018, pp. 201–205.

- Jianwei Zhang, Yajun Li, Tao Han, Jinghu Li., Radiation Hardened Design Based on TMR-5DFF for ASIC, *IEEE 5th International Conference on Computer and Communications (ICCC)*, 2019, pp. 981–986.

- 7. Danilov I.A., Gorbunov M.S., Antonov A.A., SET Tolerance of 65 nm CMOS Majority Voters: A Comparative Study, *IEEE Transactions on Nuclear Science*, 2014, vol. 61, pp. 1597–1602.

- 8. Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W., Layout technique for single-event transient mitigation via pulse quenching, *IEEE Transactions on Nuclear Science*, 2011, vol. 58, no. 3, pp. 885–890.

- 9. Garg R., Khatri S.P., *Analysis and design of resilient VLSI circuits: Mitigating soft errors and process variations.* New York: Springer, 2010. pp. 194–205.