### АВТОМАТИКА И ЭЛЕКТРОНИКА

УЛК 621.382+621.396.6

# КОМПЕНСАЦИЯ ИМПУЛЬСОВ ПОМЕХ В ТРОИЧНОМ КМОП МАЖОРИТАРНОМ ЭЛЕМЕНТЕ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ И-НЕ ПРИ ВОЗДЕЙСТВИИ ОДИНОЧНЫХ ИОНИЗИРУЮЩИХ ЧАСТИЦ

© 2019 г. Ю. В. Катунин<sup>1,\*</sup>, В. Я. Стенин<sup>1,2,\*\*</sup>

<sup>1</sup> НИИ системных исследований РАН, Москва, 117218, Россия

<sup>2</sup> Национальный исследовательский ядерный университет "МИФИ", Москва, 115409, Россия

\*e-mail: katunin@cs.niisi.ras.ru

\*\*e-mail: vystenin@mephi.ru

Поступила в редакцию 19.06.2019 г.

После доработки 19.06.2019 г.

Принята к публикации 25.06.2019 г.

Представлены результаты моделирования КМОП троичного мажоритарного элемента по 65-нм объемной технологии с мерами по повышению устойчивости к импульсам помех, возникающих при воздействии одиночных ионизирующих частиц. Воздействия на каждый транзистор элемента имитируются средствами TCAD в виде сбора транзисторами заряда с трека частицы. Моделируется сбор заряда с треков с направлением по нормали к поверхности кристалла. Линейная передача энергии на трек составляет 60 МэВ см²/мг. Исследуется КМОП троичный мажоритарный элемент, состоящий только из логических элементов И-НЕ. Применена топология с чередованием транзисторов каскадного соединения логических элементов И-НЕ, что обеспечивает повышение помехоустойчивости при сборе заряда с треков частиц. Этот элемент имеет меньше транзисторов, чем традиционный на логических элементах И и ИЛИ. Он может быть полезен при проектировании мажоритарной логики в 28—65 нм КМОП системах, устойчивых к воздействиям одиночных ядерных частиц.

*Ключевые слова:* импульс помехи, моделирование, нестационарное состояние, одиночная ядерная частица, помехоустойчивость, троичный мажоритарный элемент

**DOI:** 10.1134/S2304487X19040060

### 1. ВВЕДЕНИЕ

Результатом воздействия одиночных ядерных частиц на комбинационные логические элементы является образование импульсов помех [1], которые могут вызывать временные изменения логического состояния элемента. Повышение устойчивости к воздействиям одиночных ионизирующих частиц зависит от схем элементов и топологического их проектирования. Наиболее распространенным методом повышения помехоустойчивости комбинационной логики является тройное модульное резервирование (triple modular redundancy – TMR) [2]. При проектных нормах менее 100 нм в КМОП СБИС стало существенно проявляться диффузионное распределение заряда между транзисторами смежных логических элементов [3]. Этот эффект можно использовать при проектировании топологии логических элементов для корррекции импульса помехи с помощью частичного его гашения и в мажоритарной логике [4]. Это было успешно использовано в КМОП комбинационной логике суммирования

выходных сигналов ассоциативных ячеек памяти буфера трансляции адресов [5]. Как альтернативное решение задачи повышения помехоустойчивости, требующее детального исследования, является использование С-элементов для построения самокорректирующихся элементов многопоточной логики с тройным модульным резервированием [6]. Цель данной работы в получении количественных оценок помехоустойчивости троичного мажоритарного элемента путем виртуального экспериментального исследования средствами TCAD.

#### 2. ЭЛЕМЕНТ С МАЖОРИТАРНОЙ ЛОГИКОЙ

При тройном модульном резервировании (TMR) элементы трех идентичных логических фаз используются для дублирующего вычисления одной логической функции. При возникновении помех от одиночных ионизирующих частиц выходные сигналы фаз могут отличаться. Троичные мажоритарные элемены (Triple Majority Gates —

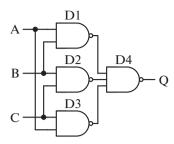

**Рис. 1.** Функциональная схема элемента с троичной мажоритарной логикой на основе только логических элементов И-НЕ.

ТМG) используются для выбора правильного выходного сигнала по логике совпадения, по крайней мере, двух из трех входных сигналов ТМG элемента. Однако и сами ТМG элементы чувствительны к воздействиям одиночных ионизирующих частиц. Актуальна задача повышения сбоеустойчивости ТМG элементов при одновременном повышении быстродействия и снижении аппаратурных затрат в мажоритарном элементе. С этой точки зрения представляет интерес ТМG элемент на основе только КМОП логических элементов И-НЕ, который содежит 18 транзисторов. На рис. 1 проведена функциональная схема ТМG элемента из трех логических элементов 2И-НЕ и одного элемента 3И-НЕ.

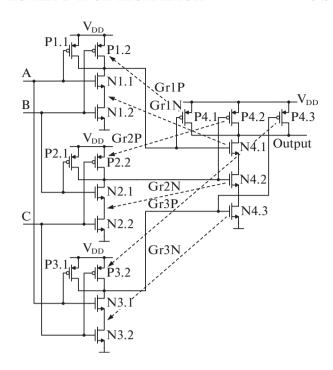

На рис. 2 представлена схема троичного мажоритарного элемента на основе трех традиционных логических элементов 2И-НЕ и одного элемента ЗИ-НЕ, выполненных на КМОП транзисторах. Используя топологию с чередованием на кристалле транзисторов одного типа канала из каскадно включенных логических элементов, можно обеспечить ими совместный сбор заряда с трека одиночной ядерной частицы. Такое совместное расположение транзисторов должно обепечить их зарядовую связь и коррекцию импульсов помех. Штриховые линии со стрелками на рис. 2 указывают на требуемые зарядовые связи транзисторов логических 2И-НЕ элементов D1, D2, D3 и 3И-НЕ элемента D4 для такой коррекции.

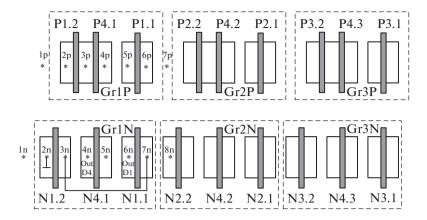

На рис. 3 приведен эскиз топологии троичного мажоритарного элемента с чередованием транзисторов трех логических элементов 2И-НЕ и одного элемента 3И-НЕ. Все транзисторы расположены в шести группах, при этом имеются три одинаковые по составу группы NMOП транзисторов (Gr1N–Gr3N) и три одинаковые группы PMOП транзисторов (Gr1P–Gr3P). В такой компоновке, на примере групп транзисторов Gr1N и Gr1P, следует, что в группе Gr1N транзистор N4.1 элемента D4 расположен между транзистор P4.1 элемента D4 расположен между транзистор P4.1 элемента D4 расположен между транзистор

**Рис. 2.** Схема троичного мажоритарного элемента на основе трех логических элементов 2И-НЕ и одного элемента 3И-НЕ.

рами P1.1 и P1.2 элемента D1. Подобным образом образованы и группы Gr2N, Gr3N и Gr2P, Gr3P.

#### 3. МЕТОДИКА МОДЕЛИРОВАНИЯ

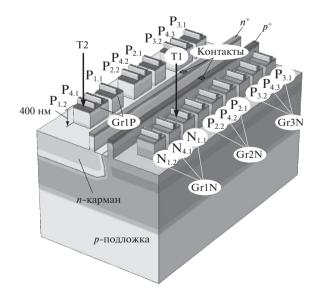

На рис. 4 приведена 3D TCAD (Technology computer-aided design) приборная физическая модель троичного мажоритарного элемента (TMG) на основе логических И-НЕ элементов D1, D2, D3 и D4 (рис. 1). Это приборная модель содержит шесть групп транзисторов Gr1N-Gr3N и Gr1P-Gr3P. Все транзисторы окружены неглубокой 400 нм траншейной диоксидной изоляцией, которая на рис. 4 удалена, чтобы более четко представлять взаимное расположение транзисторов в группах. В каждую группу входят два транзистора элемента 2И-НЕ и один транзистор того же типа проводимости из элемента 3И-НЕ, затвор которого подключен к выходу элемента 2И-НЕ в соответствии со схемой на рис. 2.

Переходные процессы в нестационарных состояниях логических элементов при сборе заряда с трека одиночной частицы, исследуемые в ТМС элементах при трехмерном моделировании средствами ТСАD, зависят от линейной передачи энергии частицей на трек (linear energy transfer — LET) [1] и направления трека. В работе использованы треки с направлениями вдоль нормали к поверхности приборной части модели (на рис. 4 примеры треков Т1 и Т2). Используются треки с линейной передачей энергии на них 60 МэВ см²/мг,

**Рис. 3.** Эскиз топологии троичного мажоритарного элемента с чередованием транзисторов трех логических элементов 2И-НЕ и одного элемента 3И-НЕ.

что соответствует максимуму диапазона LET, наиболее часто используемого для экспериментального исследования сбоеустойчивости элементов СБИС при воздейстаии тяжелых заряженных частиц [7, 8].

Трехмерная приборная физическая модель разработана на основе моделей транзисторов, представленных в работе [9]. Ширина N- и РМОП-транзисторов составляет 400 нм. Результаты получены с помощью имитатора Sentaurus при температуре 25°С и напряжении питания 1.0 В для структуры по 65 нм КМОП объемной технологии.

Поскольку по составу транзисторов и топологии группы Gr1N-Gr3N одинаковы, как одинаковы и группы Gr1P-Gr3P, то приведены результаты моделирования помех и их коррекции при сборе заряда с трека только для пары групп Gr1N, Gr1P, образованных из транзисторов логических элементов D1 и D4 (рис. 1).

#### 4. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ

Линейная передача энергии от частицы к треку составляет 60 МэВ см²/мг. Направления треков вдоль нормали к поверхности приборной модели (на рис. 4 примеры треков Т1 и Т2). Шаг смещения точек входов треков составляет 0.25 мкм и они проходят через стоковые и истоковые области транзисторов (рис. 3). Амплитуды импульсов помех определялись по максимуму отклонения напряжения узла ТМG элемента от стационарного логического уровня узла, а длительность помехи — как длительность отклонения на уровне 0.7 В от стационарного логического уровня.

### А. Образование помех в группе Gr1N при входах TMG элемента A = B = C = 0

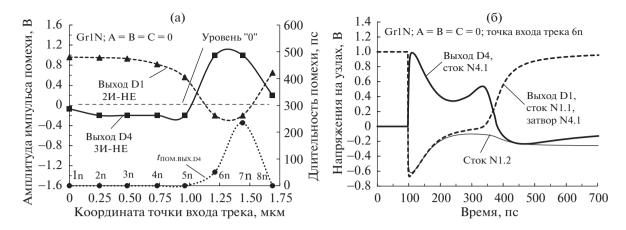

Значения параметров импульсов помех как отклонений напряжений на узлах ТМС элемента

(выходы D1 и D4) от логического уровня узла и длительности импульсов помех на выходе TMG элемента  $t_{\Pi OM.B \mapsto X.D4}$  приведены для группы NMOП транзисторов Gr1N на рис. 5а при сигналах на трех входах TMG элемента A = B = C = 0 в зависимости от положения точки входа трека (рис. 3) при линейной передаче энергии частицей на трек LET = 60 M эВ см²/мг. Тонкими штриховыми линиями на рис. 5а отмечено напряжение, соответствующие уровню логического нуля "0".

Отклонения выходного сигнала (амплитуды импульсы помех) при сигналах на входах TMG элемента A = B = C = 0 незначительны и не превышают 0.2 В при точках входа трека 1n-5n и 8n. Максимальные отклонения выходного сигнала с амплитудой 1 В отмечены (см. рис. 5a) при про-

**Рис. 4.** 3D TCAD приборная физическая модель элемента троичной мажоритарной логики на основе только логических элементов И-НЕ.

**Рис. 5.** Зависимости образования импульсов помех в группе NMOП транзисторов Gr1N при сигналах на входах TMG элемента A = B = C = 0 для треков с LET =  $60 \text{ M} \rightarrow \text{B} \text{ cm}^2/\text{mr}$ : (a) амплитуды и длительности импульсов помех в зависимости от положения точки входа трека; (б) зависимости напряжений на узлах для точки входа трека 6n.

хождении трека через точку 6n (рис. 3, область стока транзистора N1.1) и через точку 7n (область истока N1.1). Это результаты сбора с треков 6n и 7n заряда транзисторами N1.1 и N4.1 при их каскадном соединении (сток N1.1 соединен с затвором N4.1, рис. 2). При амплитудах импульсов помех 1 В длительность помехи для точки входа трека 6n составляет всего 50 пс, а для точки входа 7n составляет 235 пс.

На рис. 56 приведены зависимости напряжений на выходных узлах элементов D1, D4 для случая совместного сбора заряда с трека ММОП транзисторами N1.1 и N4.1 элементов D1 и D4 (точка входа трека 6п на рис. 3), когда входные сигналы ТМG A = B = C = 0. Изначально запертый по затвору транзистор N1.1 начинает собирать заряд при возникновении трека с точкой входа 6n и переходит вместе с транзистором N1.2 в инверсное состояние с напряжением -0.6 В на стоке N1.1, запирая по затвору транзистор N4.1 (рис. 5б). Сбор заряда запертым транзистором N4.1 снижает напряжение на его стоке и выходе D4 (3И-HE). После 50 пс сбора заряда напряжение на стоке транзистора N4.1 становится меньше 0.7 В, что сохраняет выходной логический сигнал элемента ТМС на уровне, близком к "0", и исключает ложное воздействие на последующие логические элементы. Это случай коррекции (минимизации) амплитуды, а также длительности импульса помехи до уровня 50 пс по уровню 0.7 В от пьедестала импульса.

### Б. Образование помех в группе Gr1N при входах TMG элемента A = B = 1, C = 0

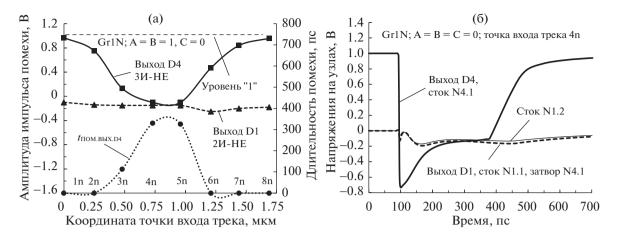

Значения параметров импульсов помех как отклонений напряжений на узлах TMG элемента (выходы D1 и D4) от логического уровня узла и длительности импульсов помех на выходе TMG элемента  $t_{\Pi OM, B \mapsto X, D4}$  приведены для группы NMOП транзисторов Gr1N на рис. 6а при сигналах на трех входах ТМG элемента A = B = 1, C = 0. При этих сигналах на входах ТМС элемента значительные отклонения выходного сигнала (импульсы помех) наблюдаются при сборе заряда запертым NMOП транзистором N4.1 в группе транзисторов Gr1N (рис. 6a) (точки входа трека 3n-5n). При этих точках входа трека транзисторы N1.1, N1.2 элемента D1 (2И-НЕ) переходят в начале сбора заряда с трека в инверсный режим смещения с отрицательным напряжением на стоках, что запирает транзистор N4.1 элемента D4, который, собирая с этом режиме заряд, тоже переходит в инверсное смещение с напряжением на его стоке -0.7 В. Это фиксирует состояние логического нуля "0" на выходе ТМС элемента при точках входа трека 3n-5n. Отклонения от логическоимпульсного уровня на выходе элемента ТМС при этом имеют значения 0.9-1.1 В при длительностях импульсов помех 100-330 пс.

На рис. 6б приведен пример зависимостей напряжений па узлах ТМG элемента при сборе заряда с трека с точкой входа 4n (рис. 3), когда входные сигналы A = B = 1, C = 0. Изначально открытые транзисторы N1.1 и N1.2 в начале сбора заряда переходят в инверсный режим смещения при напряжении на стоках -(0.16-0.1) В, что поддерживает запертый по затвору транзистор N4.1 в этом состоянии. Транзистор N4.1 собирает заряд и формирует на выходе ТМG элемента импульсошибки с амплитудой 1 В и длительностью 330 пс, равной времени сбора заряда. Для входных точек трека 3n и 5n результаты формирования импульса ошибки аналогичны (рис. 66). В этом случае нет коррекции импульса помехи.

**Рис. 6.** Зависимости образования импульсов помех в группе NMOП транзисторов Gr1N при сигналах на входах TMG элемента A = B = 1, C = 0 для треков с LET = 60 MэB см<sup>2</sup>/мг: (а) амплитуды и длительности импульсов помех TMG элемента в зависимости от положения точки входа трека; (б) зависимости напряжений на узлах для точки входа трека 4n.

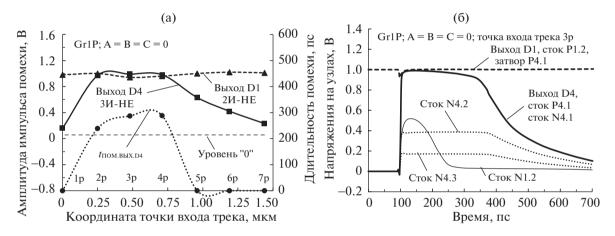

**Рис. 7.** Зависимости образования импульсов помех в группе РМОП транзисторов Gr1P при сигналах на входах TMG элемента A = B = C = 0 для треков с LET =  $60 \text{ M} \Rightarrow \text{B cm}^2/\text{mr}$ : (a) амплитуды и длительности импульсов помех в зависимости от положения точки входа трека; (б) зависимости напряжений на узлах для точки входа трека 3р.

### В. Образование помех в группе Gr1P при входах TMG элемента A=B=C=0

Значения амплитуд импульсов помех на узлах ТМG элемента (выходы D1 и D4) и длительности импульсов помех на выходе ТМG элемента приведены для группы РМОП транзисторов Gr1P на рис. 7а при сигналах на входах ТМG элемента A = B = C = 0 и линейной передаче энергии на трек LET =  $60 \text{ M} \cdot \text{B} \text{ cm}^2/\text{Mr}$ . При входах A = B = C = 0 значительные амплитуды импульсов помех наблюдаются в группе транзисторов Gr1P (рис. 7а) при сборе заряда с треков с точками входа 2p-4p.

На рис. 76 приведен пример зависимостей напряжений на узлах ТМС элемента при сборе заряда с трека с точкой входа 3р в область общих истоков РМОП транзисторов Р1.2 и Р4.1 (рис. 3) из D1 и D4 элементов, когда входные сигналы ТМС

А = В = С = 0. Входные сигналы поддерживают транзисторы P1.2 и P1.1 открытыми во время сбора заряда, что сохраняет изначально запертый транзистор P4.1 в этом состоянии, и он собирает заряд с трека с точкой входа 3р, формируя на выходе элемента TMG импульс ошибки с амплитудой 1 В и длительностью 290 пс. Амплитуды помех на выходе TMG элемента для точек входа трека 2p—4р имеют значения 1.0 В при длительностях помех 240—290 пс, определяемых временем сбора заряда. В этом случае нет коррекции импульса помехи на выхоле TMG элемента.

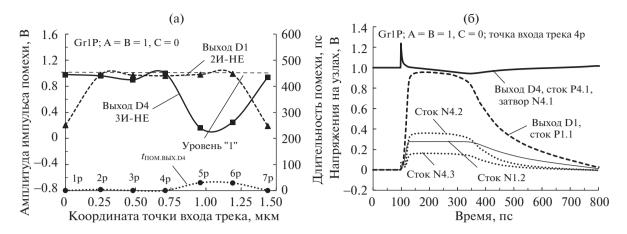

### $\Gamma$ . Образование помех в группе Gr1N при входах TMG элемента $A=B=1,\ C=0$

При сигналах на входах TMG элемента A = B = 1, C = 0 (рис. 8a) в группе Gr1N амплитуды им-

**Рис. 8.** Зависимости образования импульсов помех в группе РМОП транзисторов Gr1P при сигналах на входах TMG элемента A = B = 1, C = 0 для треков с LET =  $60 \text{ M} ext{9} \text{B cm}^2/\text{Mr}$ : (a) амплитуды и длительности импульсов помех в зависимости от положения точки входа трека; (б) зависимости напряжений на узлах для точки входа трека 4р.

пульсов помех при сборе заряда с треков с точками входа 1p—4p и 7p незначительны и не превышают 0.1 В. Для треков с точками входа 5p и 6p импульсы помех имеют амплитуды 0.75—0.84 В, но с незначительной длительностью 30 пс.

На рис. 8б приведен пример зависимостей напряжений на узлах ТМС элемента при сборе заряда с трека с точкой входа 4р в область стока РМОП транзистора P4.1 (рис. 3) элемента D4, когла вхолные сигналы TMG элемента A = B = 1. C = 0. Входные сигналы поддерживают транзисторы Р1.2 и Р1.1 запертыми во время сбора заряда, а изначально открытый транзистор Р4.1 в открытом состоянии. Транзистор Р4.1 в начале сбора заряда переходит в режим инверсного смещения и остается в состоянии с напряжением на его стоке около 1 В до конца сбора заряда с трека, что фиксирует напряжение на выходе ТМС элемента на логическом уровне "1" (рис. 8б). Закрытые по затворам входными сигналами РМОП транзисторы Р1.2 и Р1.1 собирают заряд, формируя импульс на выходе элемента D1 и затворе транзистора Р4.1. Однако, этот импульс не закрывает транзистор P4.1 и TMG элемент сохраняет на выходе логический уровень "1". Для точек входов трека 2р и 3р такие же результаты сбора заряда и выходной сигнал ТМС элемента без импульса помехи. Это случай минимизации амплитуды и длительности импульса помехи.

### 5. АНАЛИЗ РЕЗУЛЬТАТОВ МОДЕЛИРОВАНИЯ

Топология ТМС элемента только на логических элементах И-НЕ с разделением транзисторов на группы, в которых объединены транзисторы из каскадно соединенных элементов И-НЕ, позволяет повысить помехоустойчивость путем

коррекции импульсов помех при сборе заряда с треков одиночных ионизирующих частиц.

В том случае, когда транзистор N4.1 при входах A = B = C = 0 (рис. 5a) или транзистор P4.1 при A = B = 1, C = 0 (рис. 8a) элемента D4 открыты, собирая заряд с трека и переходя в запертое состояние, могут минимизировать импульс помехи на выходе TMG элемента.

В том случае, когда транзистор N4.1 при A = B = 1, C = 0 (рис. 6a) или транзистор P4.1 при A = B = C = 0 (рис. 7a) элемента D4 заперты, а другие транзисторы в их группе открыты, оставаясь в исходном логическом состоянии, то закрытые транзисторы N4.1 или P4.1, собирая заряд, формируют импульс ошибки на выходе TMG элемента.

При изменении сигналов на входах ТМС элемента часть или все транзисторы логических элементов 2И-НЕ и 3И-НЕ меняют электрический режим смещения, переходя из запертого состояния в открытое и наоборот. Это приводит к изменению характера сбора заряда с трека для тех же точек его входа в группах Gr1N—Gr3N и Gr1P—Gr3P и соответственно меняет характер образования помехи на выходе ТМС элемента.

Изменения при сборе заряда можно оценить по результатам моделирования, приведенным в табл. 1 для группы NMOП транзисторов Gr1N и в табл. 2 для группы PMOП транзисторов Gr1P. В табл. 1 и 2 приведены амплитуды и длительности импульсов помехи на выходе TMG элемента. Длительности определялись по уровню 0.7 В относительно пьедестала импульса, поэтому при амплитуде ниже 0.7 В длительности равны нулю и не приведены для этих случаев в табл. 1 и 2.

Для группы Gr1N из данных в табл. 1 следует, что изменение входных сигналов A=B=C=0 на A=B=1, C=0 переводит группу Gr1N из состо-

NMOII TRANSPORTED Gr1N

Таблица 1. Амплитуды и длительности импульсов помехи на выходе ТМС элемента, образующиеся в группе

| Temori Tpansuctopos GTTV                     |            |            |              |              |              |             |              |  |  |  |  |  |

|----------------------------------------------|------------|------------|--------------|--------------|--------------|-------------|--------------|--|--|--|--|--|

| Положение точки входа<br>трека в группе Gr1N | 1 <i>n</i> | 2 <i>n</i> | 3 <i>n</i>   | 4 <i>n</i>   | 5 <i>n</i>   | 6 <i>n</i>  | 7 <i>n</i>   |  |  |  |  |  |

| Hа входах ТМ $G$ $A = B = C = 0$             | 0.1 B      | 0.2 B      | 0.2 B        | 0.2 B        | 0.2 B        | 1.0 В/50 пс | 1.0 В/235 пс |  |  |  |  |  |

| На входах ТМG $A = B = 1, C = 0$             | 0          | 0.3 B      | 0.9 В/100 пс | 1.1 В/330 пс | 1.1 В/330 пс | 0.5 B       | 0.15 B       |  |  |  |  |  |

Таблица 2. Амплитуды и длительности импульсов помехи на выходе ТМС элемента, образующиеся в группе РМОП транзисторов Gr1P

| Положение точки входа <br>трека в группе Gr1P | 1 <i>p</i> | 2 <i>p</i>   | 3 <i>p</i>   | 4 <i>p</i>   | 5 <i>p</i>   | 6 <i>p</i>   | 7 <i>p</i> |

|-----------------------------------------------|------------|--------------|--------------|--------------|--------------|--------------|------------|

| Hа входах ТМ $G$ $A = B = C = 0$              | 0.2 B      | 1.0 В/240 пс | 1.0 В/290 пс | 1.0 В/290 пс | 0.63 B       | 0.42 B       | 0.2 B      |

| На входах ТМ $G A = B = 1, C = 0$             | 0          | 0            | 0.1 B        | 0            | 0.84 В/30 пс | 0.75 В/30 пс | 0          |

яния, когда помехи при сборе заряда с треков практически не образуются, в состояние, когда при точках входа треков 3n, 4n и 5n образуются помехи с амплитудами 0.87-1.1 В и длительностями 100-330 пс.

При таком же изменении входных сигналов A = B = C = 0 на A = B = 1, C = 0 группа Gr1P (табл. 2) из состояния, когда при точках входа треков 2р, 3р и 4р образуются помехи с амплитудами 1.0 В и длительностями 240-290 пс, переходит в состояние, когда помех при сборе заряда с треков практически нет.

Эти изменения обусловлены взаимодействием транзисторов логических элементов D1 и D4, объелиненных в группы Gr1N и Gr1P, которые собирают одновременно заряд с трека. Это транзисторы N1.2, N4.1, N1.1 в группе Gr1N и транзисторы P1.2, P4.1, P1.1 в группе Gr1P. Переход групп из состояния с образованием помех в состояние без помех связан с эффектом коррекции импульса помехи. Коррекция импульса помехи отсутствует в ТМС элементе с традиционной топологией без чередования транзисторов логических элементов D1, D1, D1 и элемента D4, что приводит к существенным импульсам помех, возникают во всех вариантах сигналов на входах этого ТМС элемента.

### 6. ЗАКЛЮЧЕНИЕ

КМОП троичный мажоритарный элемент только на логических элементах И-НЕ при использовании топологии с чередованием транзисторов каскадного соединения логических элементов И-НЕ имеет улучшенную помехоустойчивость при сборе заряда с треков одиночных ионизирующих частиц по сравнению с обычным вариантом без чередования транзисторов элементов И-НЕ. Этот элемент имеет меньше транзисторов, чем традиционный элемент ТМС на элементах И и ИЛИ и может быть эффективно использован в троичной мажоритарной логике с резервированием в 28-65 нм КМОП вычислительных системах, устойчивых к воздействиям одиночных ядерных частиц.

### БЛАГОДАРНОСТИ

Работа выполнена при поддержке гранта РФФИ № 19-07-00651.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Soft errors in modern electronic systems // M. Nicolaidis, Ed. New York: Springer, 2011. P. 27–54.

- 2. Hindman N.D., Clark L.T., Patterson D.W., Holbert K.E. Fully automated testable design of fine-grained triple mode redundant logic // IEEE Transactions on Nuclear Science. 2011. V. 58. № 6. P. 3046–3052.

- 3. Mahatme N.N., Jagannathan S., Loveless T.D., Massengill L.W., Bhuva B.L., Wen S.-J., Wong R. Comparison of combinational and sequential error rates for a deep submicron process // IEEE Transactions on Nuclear Science. 2011. V. 58. № 6. P. 2719-2725.

- 4. Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W. Layout technique for single-event transient mitigation via pulse quenching // IEEE Transactions on Nuclear Science. 2011. V. 58. № 3. P. 885-890.

- 5. Katunin Yu.V., Stenin V.Ya. TCAD simulation of the 65-nm CMOS logical elements of the decoders with single-event transients compensation // in Proc. of 2018 Workshop on Electronic and Networking Technologies (MWENT). Moscow, 2018. P. 1-6.

- 6. Ramamurthy C., Gujja A., Vashishtha V., Chellappa S., Clark L. T. Muller C-element self-corrected triple modular redundant logic with multithreading and low power modes // in the RADECS-3017 Conference Papers. in IEEE Xplore (Conference Section, RADECS-2017), e-book. 2019. P. 184-187.

- 7. Warren K.M., Stenberg A.L., Black J.D., Weller R.A., Reed R.A., Mendenhall M.H., Schrimpf R.D., Mas-

- sengill L.W. Heavy ion testing and single-event upset rate prediction considerations for a DICE flip-flop // IEEE Transactions on Nuclear Science. 2009. V. 56. № 6. P. 3130–3137.

- 8. Gorbunov M.S., Dolotov P.S., Antonov A.A., Zebrev G.I., Emeliyanov V.V., Boruzdina A.B., Petrov AG., Ulanova A.V.

- Design of 65 nm CMOS SRAM for space applications: a comparative study // IEEE Transactions on Nuclear Science. 2014. V. 61. № 4. P. 1575–1582.

- 9. Garg R., Khatri S.P. Analysis and design of resilient VLSI circuits: mitigating soft errors and process variations. New York: Springer, 2010. P. 194–205.

Vestnik Natsional'nogo issledovatel'skogo yadernogo universiteta "MIFI", 2019, vol. 8, no. 4, pp. 343–351

## The Noise Pulse Compensation in the Ternary CMOS Majority Element on NAND Logical Elements under Impacts of Single Ionizing Particles

Yu. V. Katunin<sup>a,#</sup> and V. Ya. Stenin<sup>a,b,##</sup>

<sup>a</sup> Scientific Research Institute of System Analysis, Russian Academy of Sciences, Moscow, 117218 Russia

<sup>b</sup> National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Moscow, 115409 Russia

<sup>#</sup>e-mail: katunin@cs.niisi.ras.ru

<sup>##</sup>e-mail: vystenin@mephi.ru

Received June 19, 2019; revised June 19, 2019; accepted June 25, 2019

**Abstract**—A CMOS ternary majority element of 65 nm bulk technology has been simulated with measures to improve the resistance to noise pulses arising under the influence of single ionizing particles. The impact on the transistors of the element has been modeled with TCAD tools in the form of the collection of the charge from the track of the particle. Charge collection from tracks with normal direction to the crystal surface is simulated. The linear energy transfer to the track is 60 MeV cm²/mg. The CMOS ternary majority element based only on NAND logical elements has been studied. Its topology is based on the interleaving transistors of the cascade connection of NAND logical elements, which provides increased noise immunity to the impacts of single particles. This ternary majority element has fewer transistors than the standard elements based on AND and OR logical gates. It can be useful to design the majority logic of the elements of 28–65 nm CMOS bulk systems that are resistant to the effects of single nuclear particles.

Keywords: error pulse, simulation, unsteady state, single nuclear particle, noise immunity, ternary majority element

DOI: 10.1134/S2304487X19040060

#### **REFERENCES**

- Soft errors in Modern Electronic Systems // M. Nicolaidis, Ed. New York: Springer, 2011, pp. 27–54.

- Hindman N.D., Clark L.T., Patterson D. W., Holbert K.E. Fully automated testable design of fine-grained triple mode redundant logic // IEEE Transactions on Nuclear Science, 2011, vol. 58, no. 6, pp. 3046—3052.

- 3. Mahatme N.N., Jagannathan S., Loveless T.D., Massengill L.W., Bhuva B.L., Wen S.-J., Wong R. Comparison of combinational and sequential error rates for a deep submicron process // *IEEE Transactions on Nuclear Science*, 2011, vol. 58, no. 6, pp. 2719–2725.

- 4. Atkinson N.M., Witulski A.F., Holman W.T., Ahlbin J.R., Bhuva B.L., Massengill L.W. Layout technique for single-event transient mitigation via pulse quenching // *IEEE Transactions on Nuclear Science*, 2011, vol. 58, no. 3, pp. 885–890.

- 5. Katunin Yu.V., Stenin V.Ya. TCAD Simulation of the 65-nm CMOS logical elements of the decoders with single-event transients compensation // in *Proc. of 2018*

- Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1–6.

- Ramamurthy C., Gujja A., Vashishtha V., Chellappa S., Clark L.T. Muller C-element self-corrected triple modular redundant logic with multithreading and low power modes // in the RADECS-3017 Conference Papers, in IEEE Xplore (Conference Section, RADECS-2017), e-book, 2019, pp. 184–187.

- 7. Warren K.M., Stenberg A.L., Black J.D., Weller R.A., Reed R.A., Mendenhall M.H., Schrimpf R.D., Massengill L.W. Heavy ion testing and single-event upset rate prediction considerations for a DICE flip-flop // *IEEE Transactions on Nuclear Science*, 2009, vol. 56, no. 6, pp. 3130–3137.

- Gorbunov M.S., Dolotov P.S., Antonov A.A., Zebrev G.I., Emeliyanov V.V., Boruzdina A.B., Petrov AG., Ulanova A.V. Design of 65 nm CMOS SRAM for space applications: a comparative study // IEEE Transactions on Nuclear Science, 2014, vol. 61, no. 4, pp. 1575–1582.

- 9. Garg R., Khatri S.P. Analysis and design of resilient VLSI circuits: mitigating soft errors and process variations. New York: Springer, 2010. pp. 194–205.